文件操作

简单有效

线性空间

BitmapDrawable

lamda表达式

.netcore

图像阴影消除

螺旋折线

st-link

Tableau

基因组学

so

百元百鸡

ldarg

vite

QIconEngine

案例

源代码

unifier

dump文件

xilinx

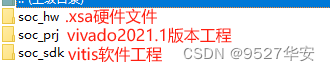

2024/4/11 22:14:52petaLinux2018.1安装、验证及启动

提示:关于petaLinux2018.1及以前版本相关,均可参考Xilinx官方文档ug1144,官方文档很详细,这里只是记载我的一些经验。 提示:后续的petaLinux2018.3等版本的安装过程类似,但还是建议先看xilinx官方文档再来看…

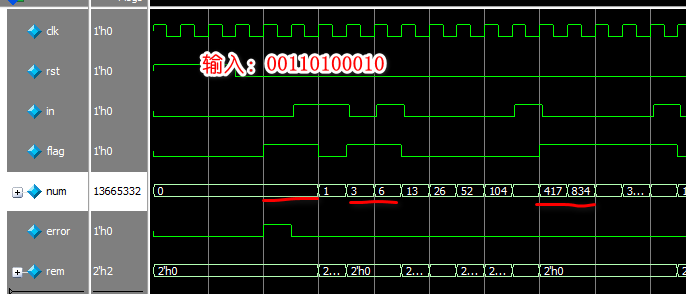

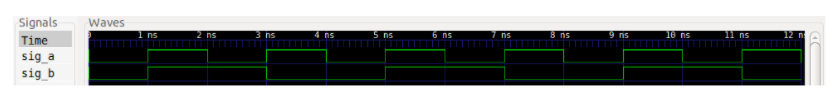

【数字IC/FPGA】手撕代码:模3检测器(判断输入序列能否被3整除)

今天我们来手撕一个常见的笔试题:模3检测,使用的方法是三段式Moore状态机。

题目描述: 输入端口是串行的1bit数据,每个时钟周期进来一位新数据后,实时检查当前序列是否能整除3,若能则输出1,否则…

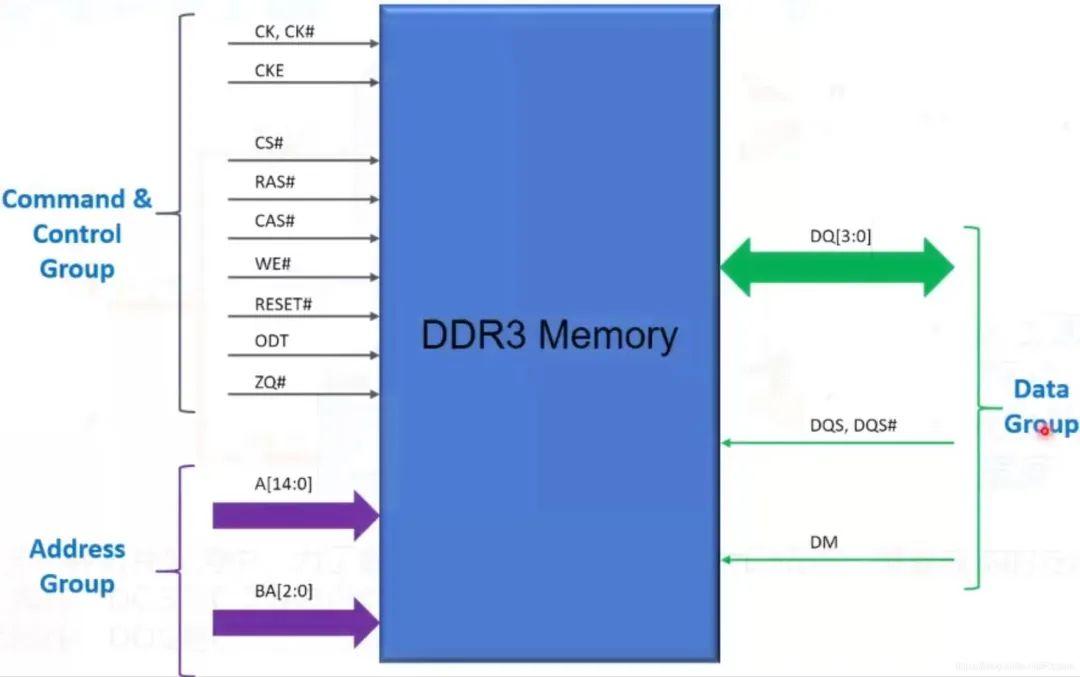

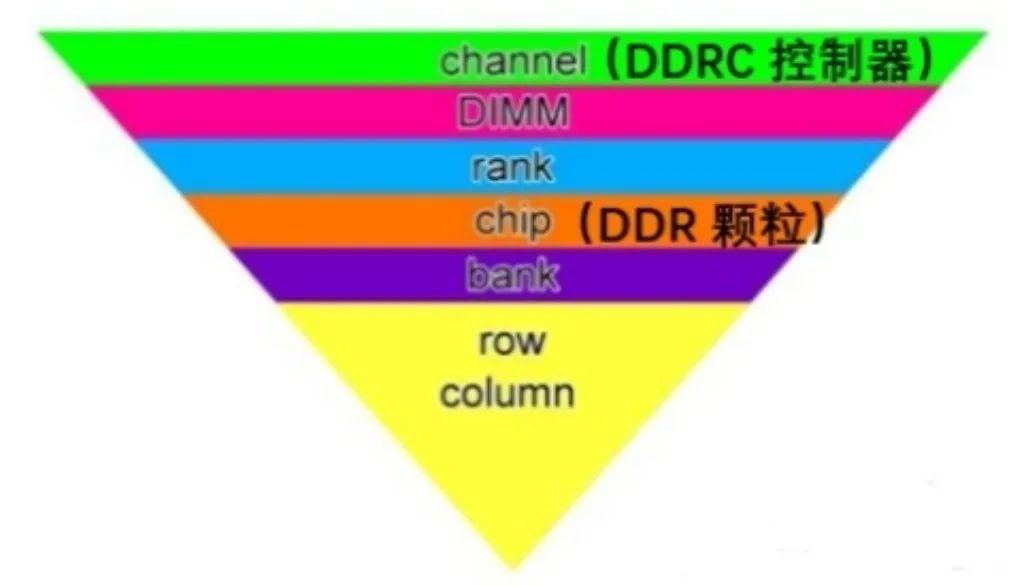

【Verilog】基于Verilog的DDR控制器的简单实现(一)——初始化

在FPGA中,大规模数据的存储常常会用到DDR。为了方便用户使用,Xilinx提供了DDR MIG IP核,用户能够通过AXI接口进行DDR的读写访问,然而MIG内部自动实现了许多环节,不利于用户深入理解DDR的底层逻辑。

本文以美光(Micro…

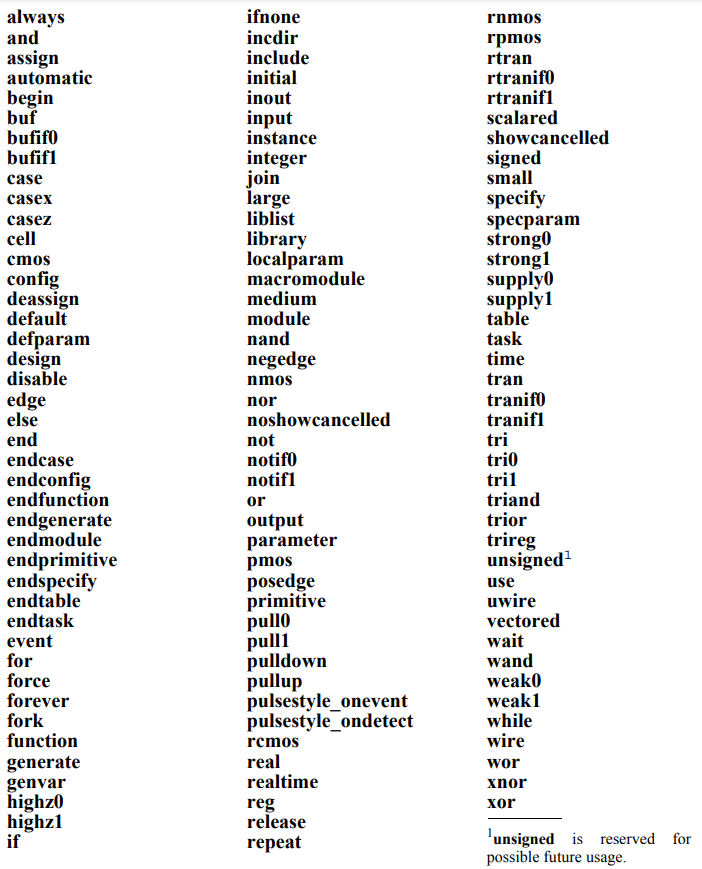

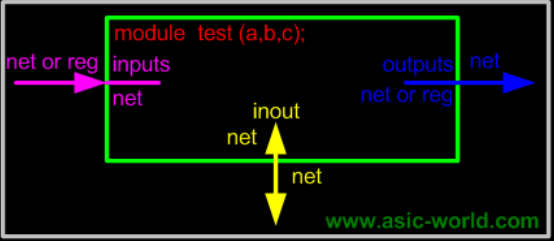

深入浅出学Verilog--基础语法

1、简介 Verilog的语法和C语言非常类似,相对来说还是非常好学的。和C语言一样,Verilog语句也是由一连串的令牌(Token)组成。1个令牌必须由1个或1个以上的字符(character)组成,令牌可以是&#x…

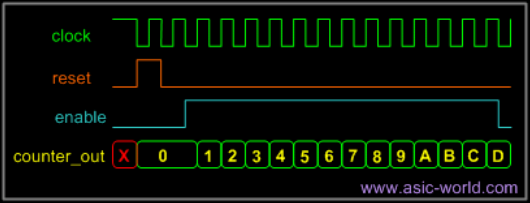

ASIC-WORLD Verilog(8)if-else语句和case语句

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…

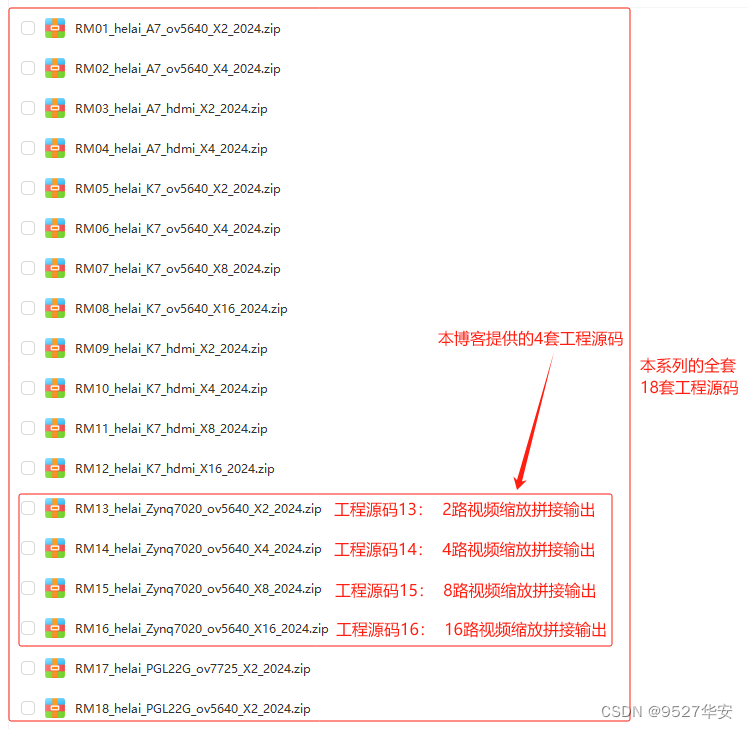

FPGA高端项目:Xilinx Zynq7020系列FPGA多路视频拼接 工程解决方案 提供6套工程源码和技术支持

目录 1、前言版本更新说明给读者的一封信FPGA就业高端项目培训计划免责声明 2、相关方案推荐我已有的FPGA视频拼接叠加融合方案本方案在Xilinx Kintex7 系列FPGA上的应用本方案在Xilinx Artix7 系列FPGA上的应用 3、设计思路框架视频源选择ov5640 i2c配置及采集动态彩条多路视频…

具于xilinx FPGA的可动态配置DDS频率控制字的DDS IP核使用例程详解

目录 1 概述2 IP examples功能3 IP 使用例程4注意事项5 DDS IP Examples下载位置 1 概述

本文用于讲解xilinx IP 的dds ip examples(动态配置频率)的功能说明,方便使用者快速上手。

2 IP examples功能

本examples 是月隐编写的针对DDS的使…

Xilinx FPGA平台DDR3设计详解(三):DDR3 介绍

本文介绍一下常用的存储芯片DDR3,包括DDR3的芯片型号识别、DDR3芯片命名、DDR3的基本结构等知识,为后续掌握FPGA DDR3的读写控制打下坚实基础。

一、DDR3芯片型号

电路板上的镁光DDR3芯片上没有具体的型号名。 如果想知道具体的DDR3芯片型号&#…

【FPGA图像处理实战】- FPGA图像处理仿真测试工程(读写BMP图片)

FPGA开发过程中“行为功能仿真”是非常必要的一个过程,如果仿真都没通过,则上板测试必定失败。

FPGA图像处理需要读写大量的图像数据,单看这些图像数据实际是没有规则的,如果直接上板测试,调试起来非常困难࿰…

XILINX 7系列FPGA Dedicated Configuration Bank功能详解

🏡《Xilinx FPGA开发指南》 目录 1,概述2,功能详解2.1,DXP_0与DXN_02.2,VCCBATT_02.3,INIT_B_02.4,M0_0,M1_0,M2_02.5,TDI,TDO,TMS,TCK2.6, VCCAD…

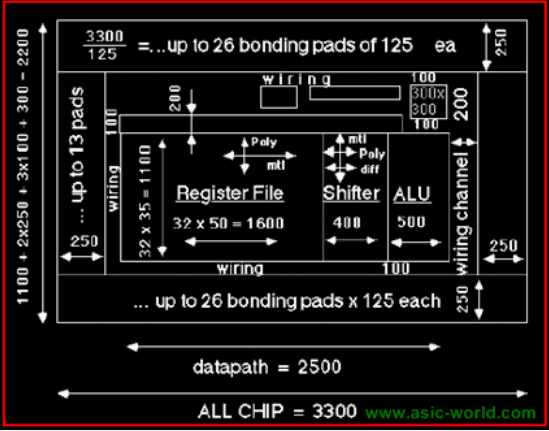

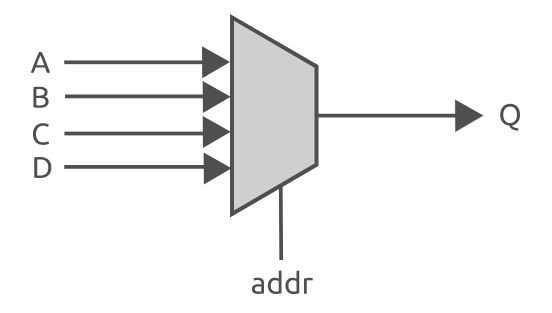

ASIC-WORLD Verilog(15)存储单元

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加点自己的理解)分享给大家。 这是网站原文&…

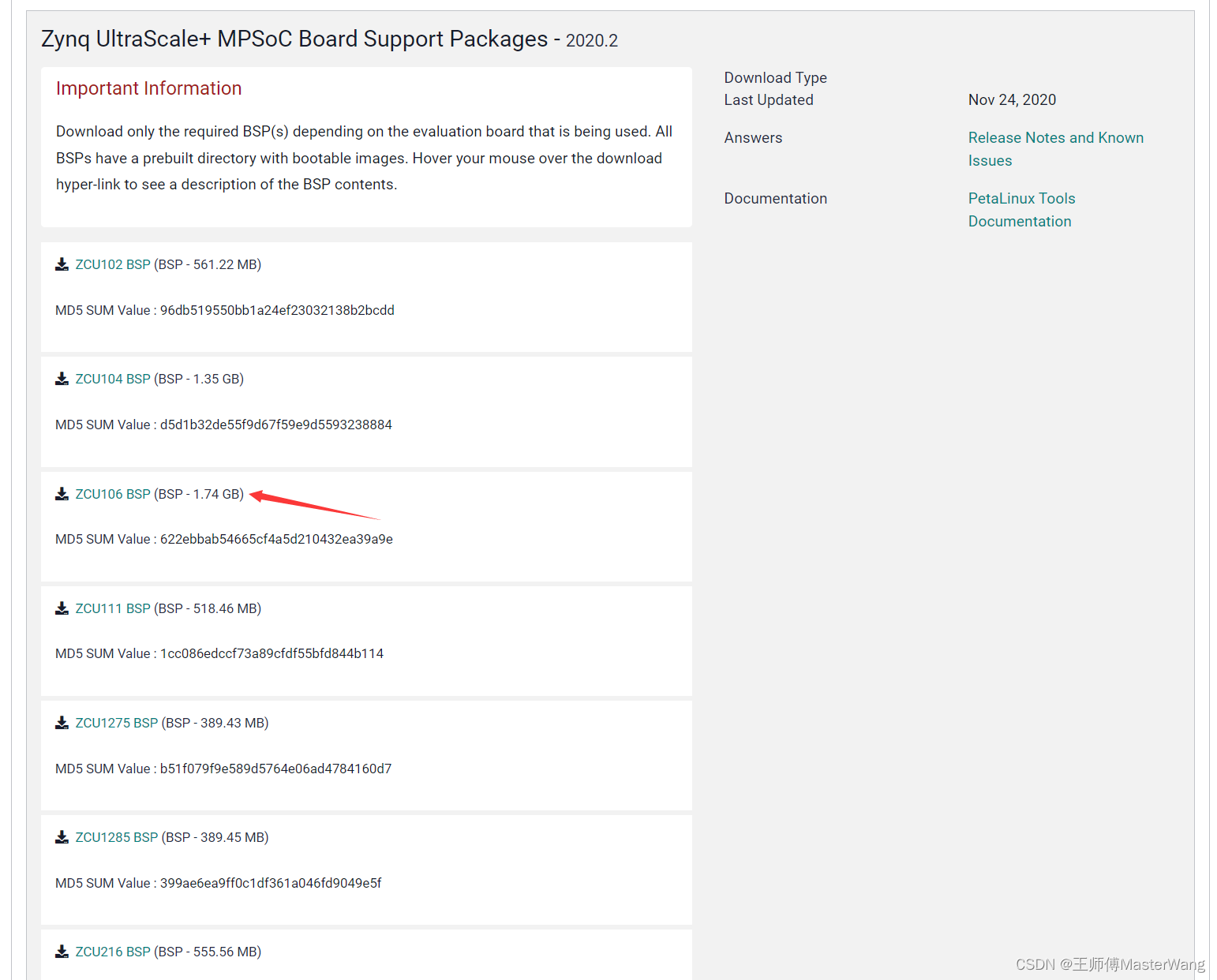

【Xilinx】基于MPSoC的OpenAMP实现(一)

【Xilinx】基于MPSoC的OpenAMP实现(一) 一、开发环境1、开发思路2、下载官方bsp包 二、编译Linux1、配置petalinux环境变量2、创建工程3、进入目录4、设置缓存目录(重点:可离线编译,加快编译速度)5、配置u-…

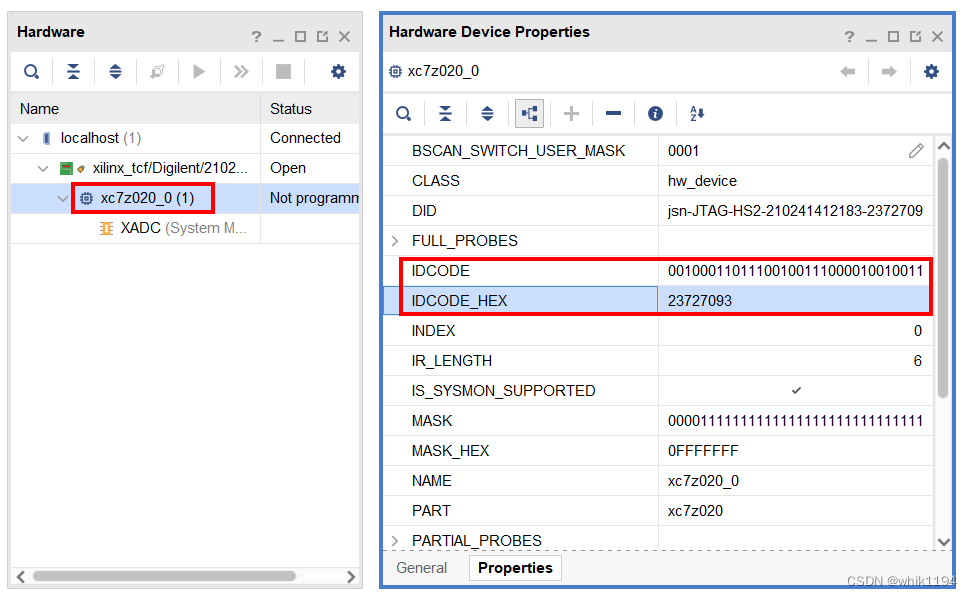

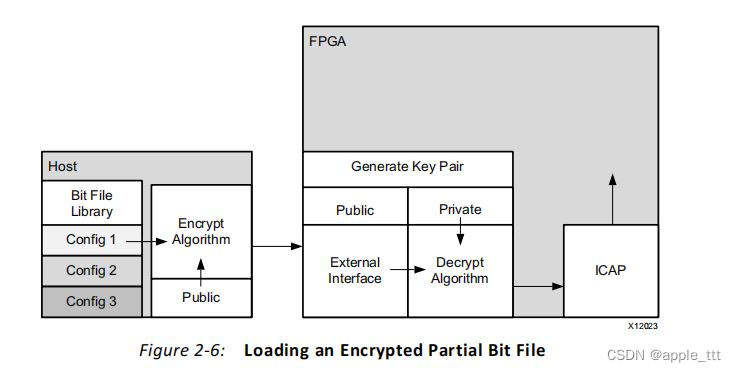

MicroBlaze系列教程(10):AXI_HWICAP的使用

文章目录 @[toc]1. AXI HWICAP简介2. MicroBlaze硬件配置3. 常用函数4. 使用示例1:读取IDCODE5. 使用示例2:从指定地址重新配置6. 参考资料本文是Xilinx MicroBlaze系列教程的第10篇文章。 1. AXI HWICAP简介

AXI_HWICAP,是把ICAP原语封装成了一个AXI接口的IP核,可以通过M…

Verilog Tutorial(8)循环语句

写在前面在自己准备写verilog教程之前,参考了许多资料----FPGA Tutorial网站的这套verilog教程即是其一。这套教程写得不错,只是没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。这是网站原文:h…

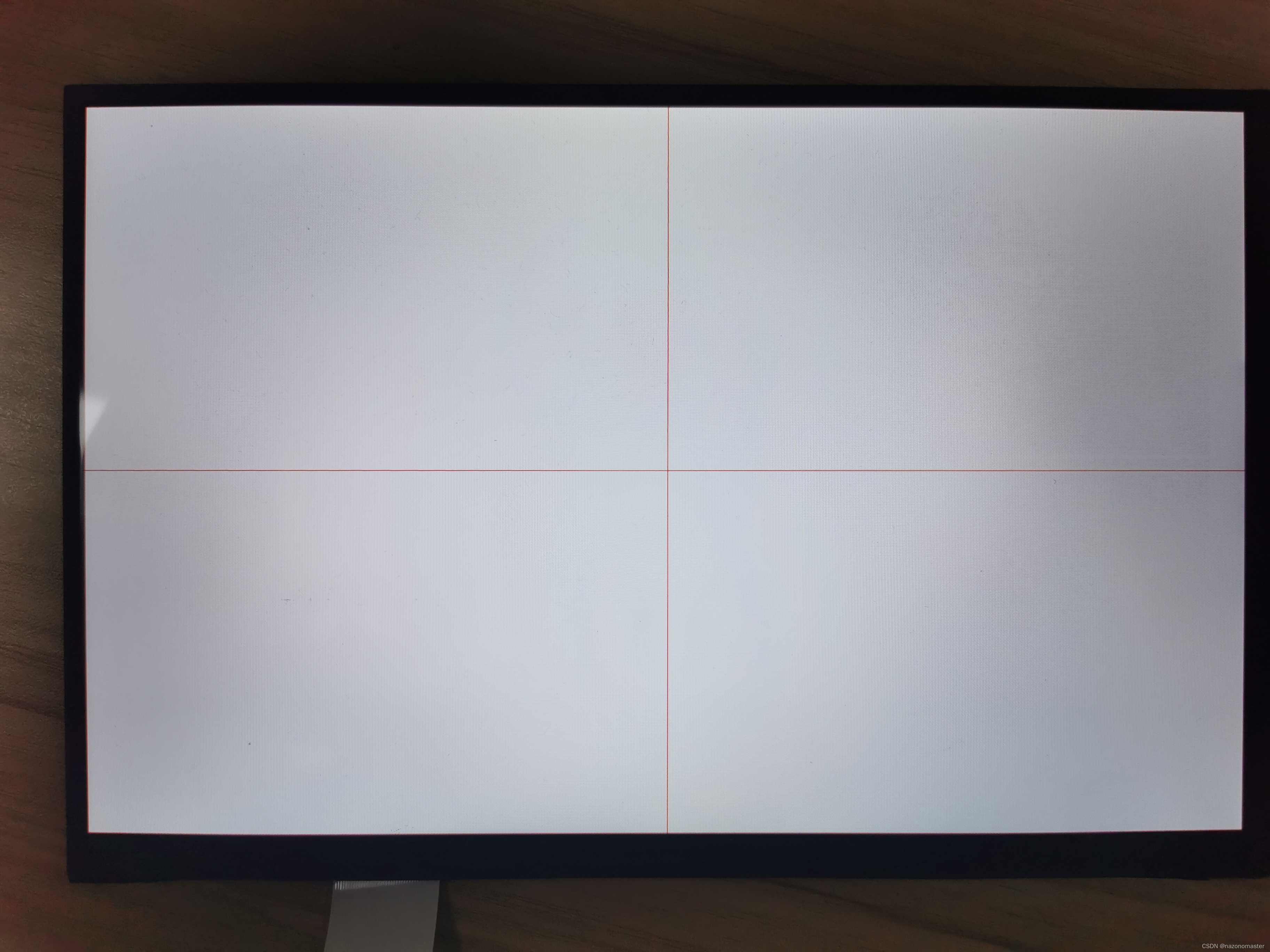

Xilinx Zynq-7000系列FPGA实现视频拼接显示,提供两套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐FPGA图像处理方案FPGA视频拼接叠加融合方案推荐 3、设计思路详解Video Mixer介绍 4、工程代码1:2路视频拼接 HDMI 输出PL 端 FPGA 逻辑设计PS 端 SDK 软件设计 5、工程代码2:4路视频拼接 HDMI 输出PL 端 FPGA 逻辑设…

【RS422】基于未来科技FT4232HL芯片的多波特率串口通信收发实现

功能简介 串行通信接口常常用于在计算机和低速外部设备之间传输数据。串口通信存在多种标准,以RS422为例,它将数据分成多个位,采用异步通信方式进行传输。 本文基于Xilinx VCU128 FPGA开发板,对RS422串口通信进行学习。 根…

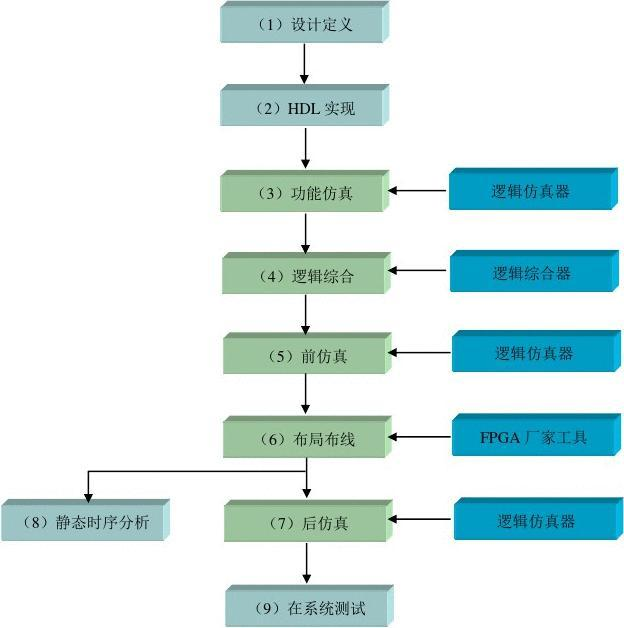

FPGA开发基本流程详解

FPGA是一种可编程逻辑器件,与传统的硬连线电路不同,它具有高度的可编程性和灵活性。FPGA的设计方法包括硬件设计和软件设计两部分,硬件设计包括FPGA芯片电路、存储器、输入输出接口电路等等,软件设计则是HDL程序开发,以…

【XILINX】记录ISE/Vivado使用过程中遇到的一些warning及解决方案

前言 XILINX/AMD是大家常用的FPGA,但是在使用其开发工具ISE/Vivado时免不了会遇到很多warning,(大家是不是发现程序越大warning越多?),并且还有很多warning根据消除不了,看着特心烦? 我这里汇总一些我遇到的…

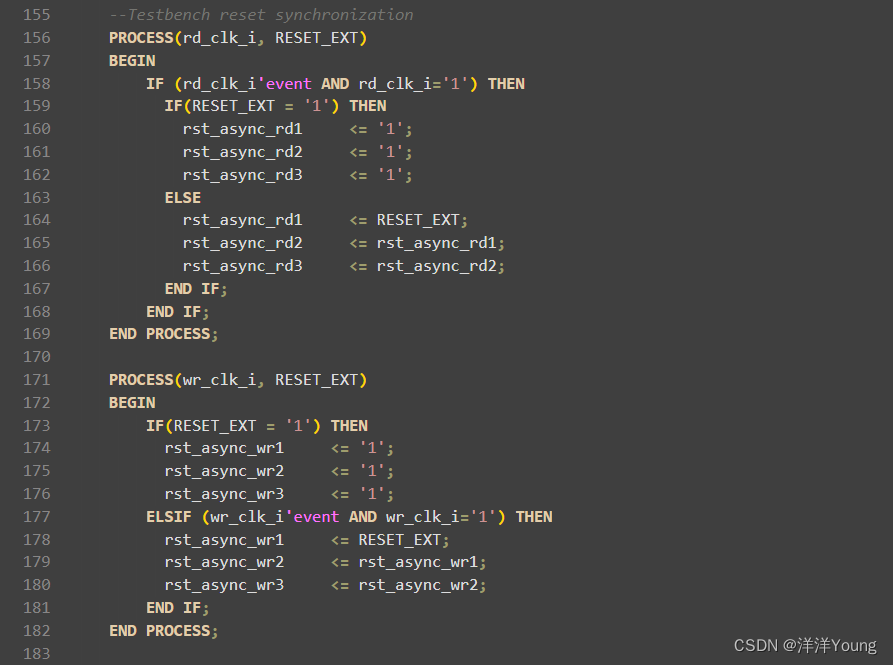

【Xilinx FPGA】异步 FIFO 的复位

FIFO(First-In-First_Out,先入先出)是一种的存储器类型,在 FPGA 开发中通常用于数据缓存、位宽转换或者跨时钟域(多 bit 数据流)。在使用异步 FIFO 时,应注意复位信号是否遵循相关要求和规范&am…

Xilinx FPGA管脚约束语法规则(UCF和XDC文件)

文章目录 1. ISE环境(UCF文件)2. Vivado环境(XDC文件) 本文介绍ISE和Vivado管脚约束的语句使用,仅仅是管脚和电平状态指定,不包括时钟约束等其他语法。

ISE使用UCF文件格式,Vivado使用XDC文件&…

跨时钟域学习记录(二)——XPM_CDC

本文以Xilinx提供的xpm_cdc代码为例,整理处理跨时钟域数据传输的常见方法。

宏定义 Xilinx定义了多个宏定义代替描述触发器行为的always块,列举如下

宏名称含义XPM_XSRREG带同步复位/置位的同步寄存器XPM_XSRREGEN带同步复位/置位和使能的寄存器XPM_XA…

Xilinx FPGA 超温关机保护

在UG480文档,有关于FPGA芯片热管理的介绍。 首先需要理解XADC中的 Over Temperature(OT)和User Temperature的关系。片上温度测量用于关键温度警告,也支持自动关机,以防止设备被永久损坏。片上温度测量在预配置和自动关…

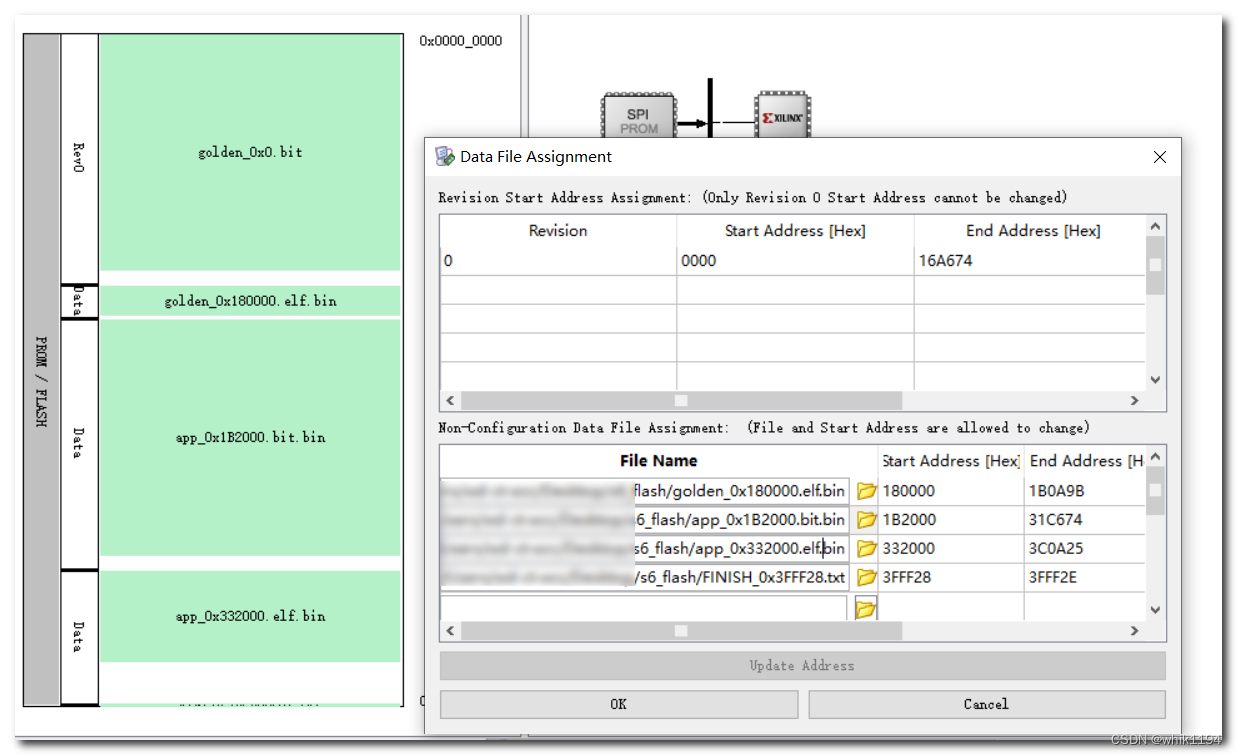

Xilinx FPGA 远程升级时bin和bit文件使用注意

以Spartan-6 ISE开发环境为例。

ISE开发环境支持生成bit和bin格式的程序文件,可以在生成选项进行配置:

把生成的bit文件和bin文件进行二进制比较,发现bit比bin文件头部多了一些内容(头部信息),剩余部分完…

Vivado:ROM和RAM的verilog代码实现

本文主要介绍ROM和RAM实现的verilog代码版本,可以借鉴参考下。

一、ROM设计方法

Read-only memory(ROM)使用ROM_STYLE属性选择使用寄存器或块RAM资源来实现ROM,示例代码如下:

//使用块RAM资源实现ROM

module rams_s…

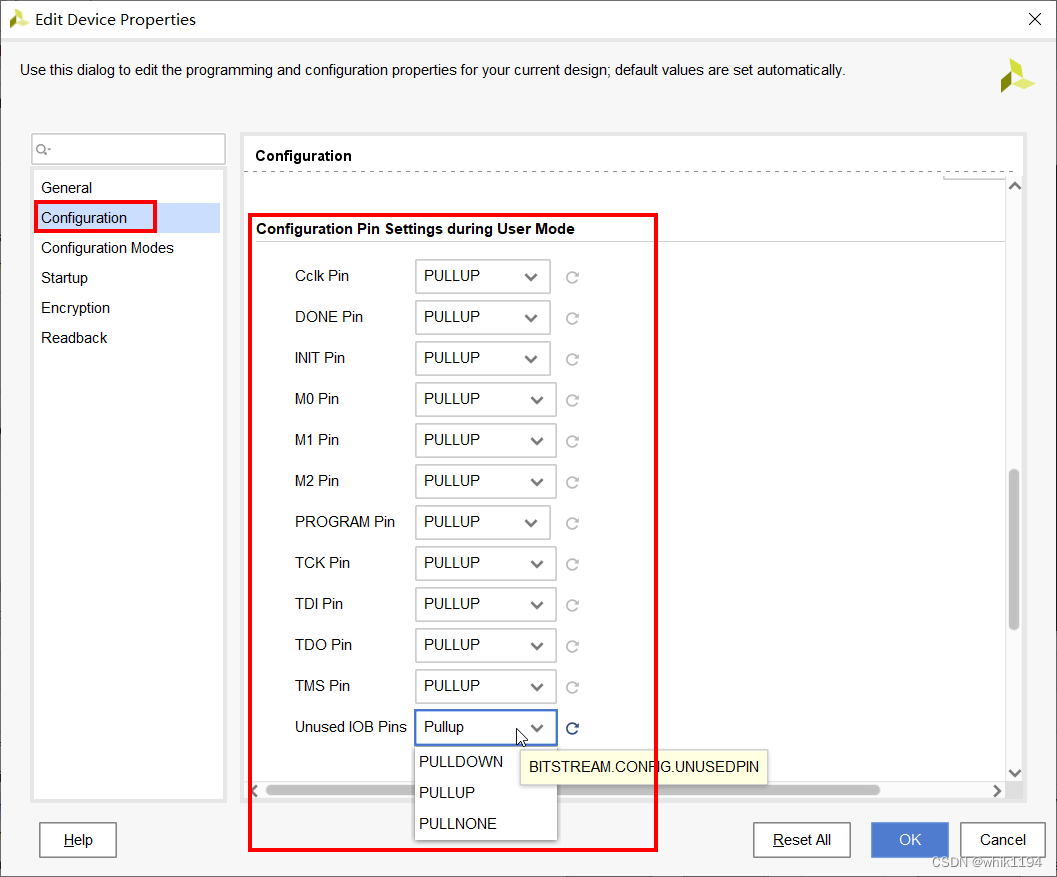

Xilinx FPGA未使用管脚上下拉状态配置(ISE和Vivado环境)

文章目录 ISE开发环境Vivado开发环境方式1:XDC文件约束方式2:生成选项配置 ISE开发环境

ISE开发环境,可在如下Bit流文件生成选项中配置。 右键点击Generate Programming File,选择Process Properties, 在弹出的窗口选…

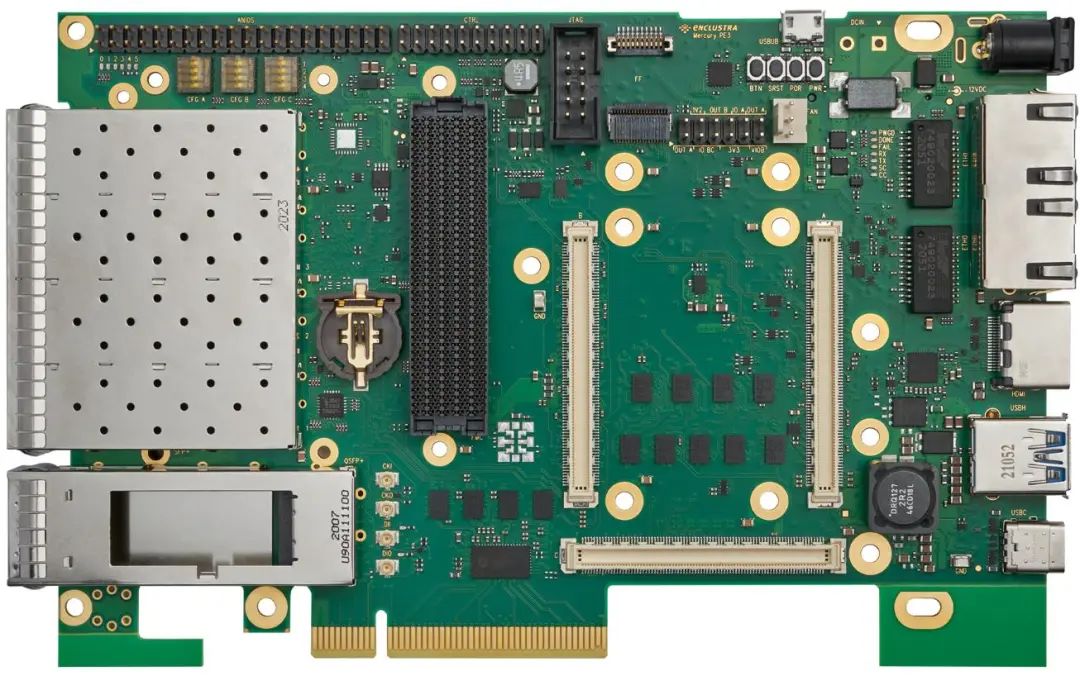

产品推荐 - 基于Xilinx Kintex-7 XC7K160T/325T/410T打造的水星Mercury+ KX2核心板

水星Mercury KX2核心板 水星Mercury KX2核心板提供高性价比的Xilinx Kintex-7 28nm FPGA和常见的接口,如USB 2.0、PCIe Gen2和千兆以太网。 KX1有强大的FPGA和标准接口、很多具备LVDS能力的I/O、大容量DDR3 SDRAM、很多高速DSP slices,它既适合高端数字信…

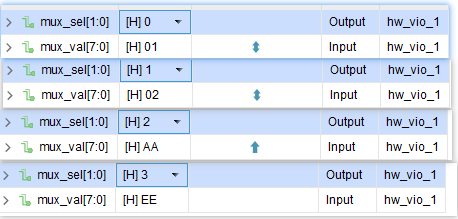

Vivado中VIO IP核的使用

Vivado中VIO IP核的使用一、写在前面二、VIO IP核配置三、VIO联调四、写在后面一、写在前面 Vivado中的VIO(Virtual Input/Output) IP核是一种用于调试和测试FPGA设计的IP核。它允许设计者通过使用JTAG接口读取和写入FPGA内部的寄存器,从而检…

[FPGA IP系列] BRAM IP参数配置与使用示例

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

本文将详细介绍Vivado中BRAM IP的配置方式和使用技巧。

一、BRAM IP核的配置

1、打开BRAM IP核

在Vivado的IP Catalog中找到B…

ASIC-WORLD Verilog(2)FPGA的设计流程

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…

Verilog Tutorial(7)If语句和Case语句

写在前面在自己准备写verilog教程之前,参考了许多资料----FPGA Tutorial网站的这套verilog教程即是其一。这套教程写得不错,只是没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。这是网站原文:h…

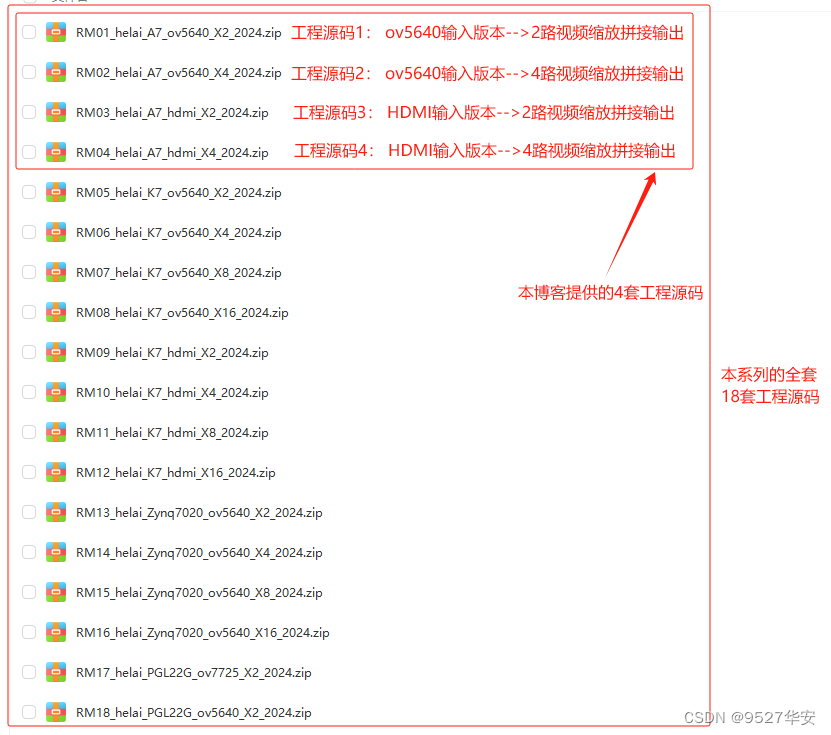

FPGA高端项目:Xilinx Zynq7020系列FPGA 多路视频缩放拼接 工程解决方案 提供4套工程源码+技术支持

目录 1、前言版本更新说明给读者的一封信FPGA就业高端项目培训计划免责声明 2、相关方案推荐我这里已有的FPGA图像缩放方案我已有的FPGA视频拼接叠加融合方案本方案的Xilinx Kintex7系列FPGA上的ov5640版本本方案的Xilinx Kintex7系列FPGA上的HDMI版本本方案的Xilinx Artix7系列…

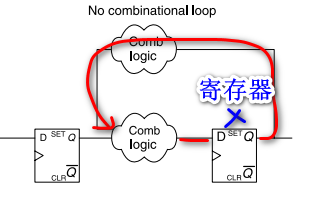

<FPGA>好的编码风格(1)--尽量避免组合逻辑环路(Combinational Loops)

什么是组合逻辑环路? 组合逻辑环路(Combinational Loops):指组合逻辑的输出信号不经过任何时序逻辑(FF等),而是直接反馈到输入节点,从而构成的电路环路。 此外,如果直接将…

【FPGA/IC】RAM-Based Shift Register Xilinx IP核的使用

前言

一般来讲,如果要实现移位寄存器的话,通常都是写RTL用reg来构造,比如1bit变量移位一个时钟周期就用1个reg,也就是一个寄存器FF资源,而移位16个时钟周期就需要16个FF,这种方法无疑非常浪费资源。

Xili…

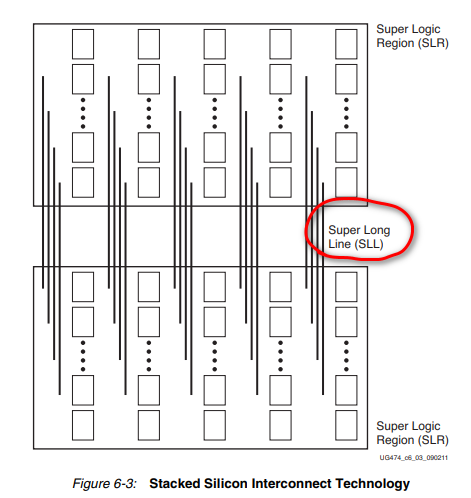

从底层结构开始学习FPGA(0)----FPGA的硬件架构层次(BEL Site Tile FSR SLR Device)

系列目录与传送门

《从底层结构开始学习FPGA》目录与传送门 Xilinx的FPGA,从硬件架构的角度可以划分为6个层次,从底层到顶层依次是:

BEL(最底层单元)SiteTileFSRSLRDevice(FPGA芯片) 接下来我…

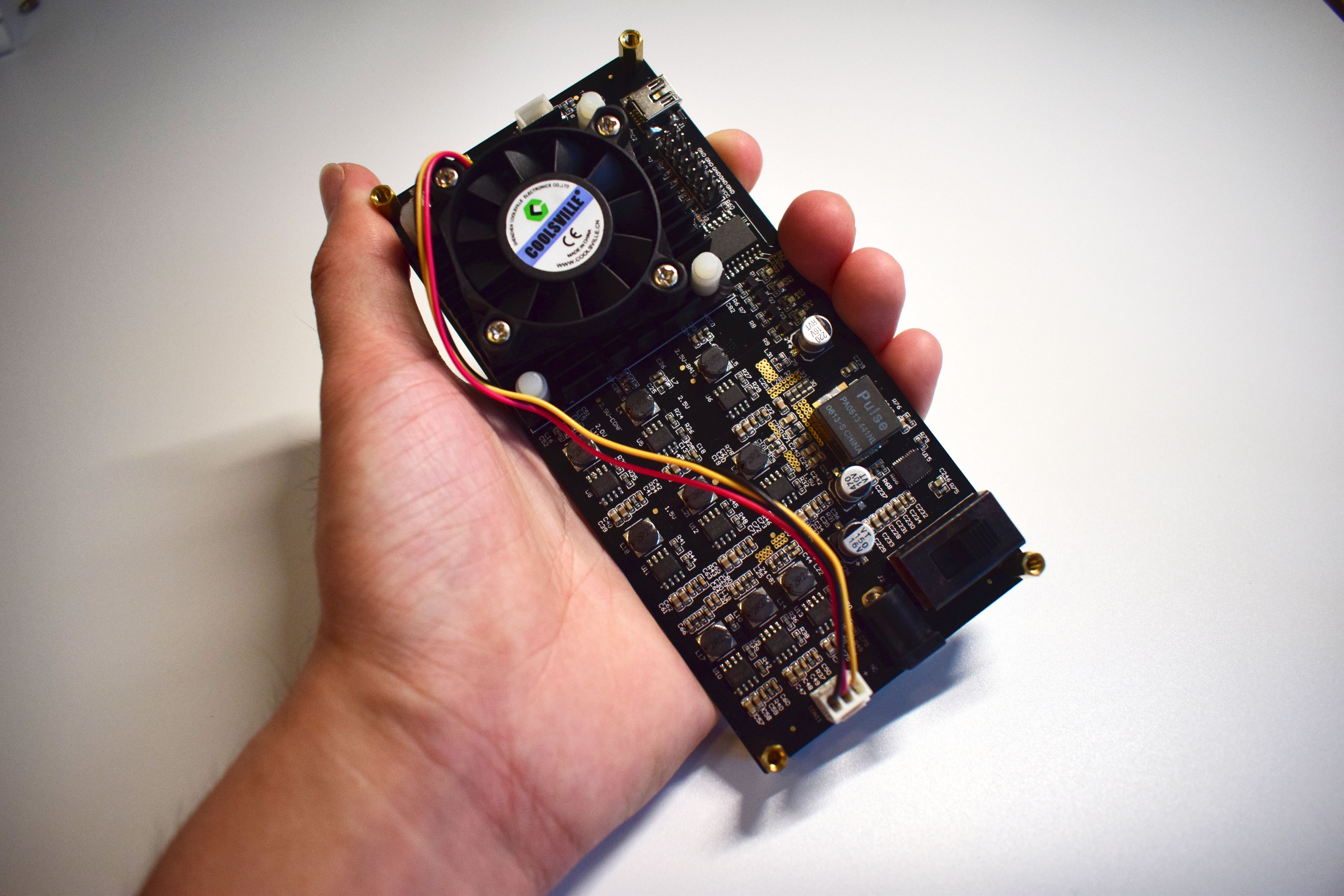

强大的JTAG边界扫描(1):基本原理介绍

文章目录 1. 什么是边界扫描?2. JTAG硬件接口3. 边界扫描相关的软硬件4. 学习资料5. 总结 我是怎么了解到边界扫描的呢?

这就要从我淘到一块FPGA板卡的事情说起了。

前段时间我在某二手平台上淘了一块FPGA板子,它长这样: 板子的…

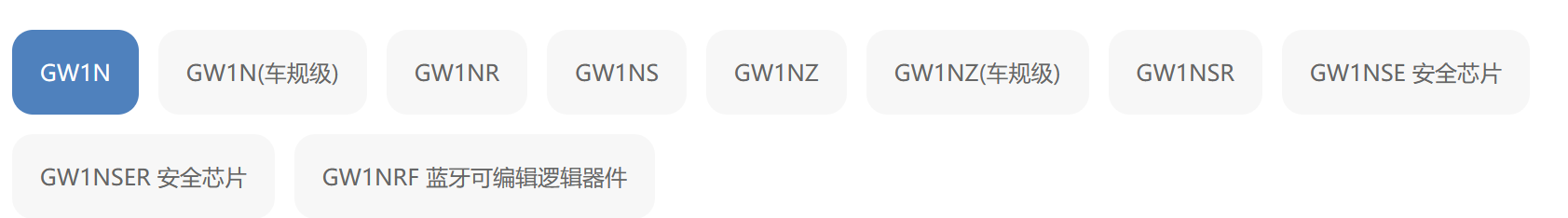

国产FPGA选型指南:如何选择适合你的国产FPGA芯片?

FPGA自1985年由Xilinx的创始人之一Ross Freeman发明后,全球90%的FPGA市场一直被国外厂家所占有,主要是这四家公司:Xilinx、Altera、Lattice、Microsemi。

Xilinx 和Altera公司占据了全球近80%以上的市场份额,且拥有着FPGA领域绝大…

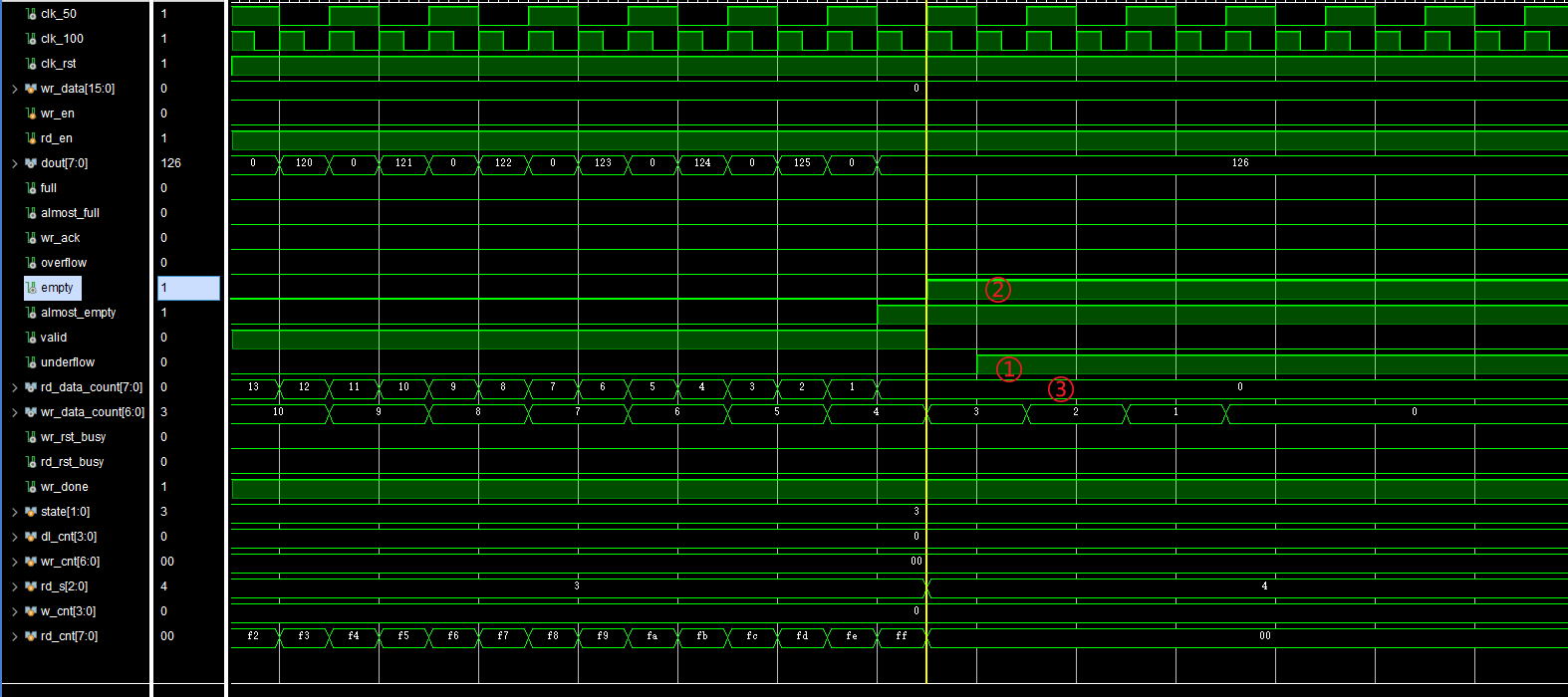

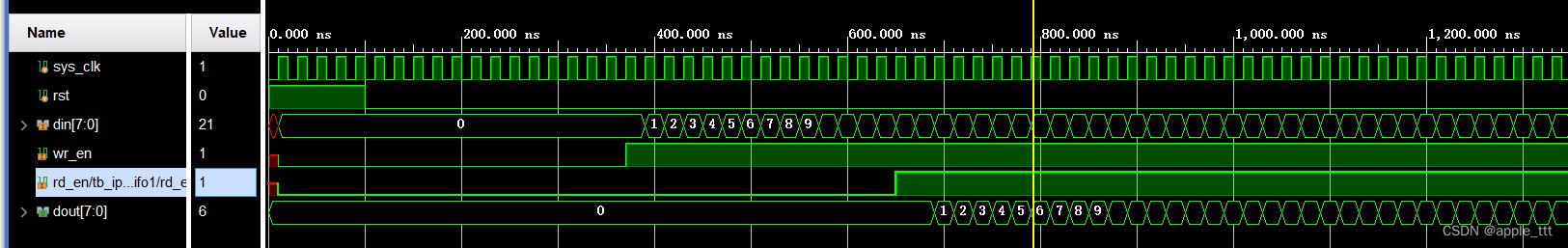

G2—FIFO IP核2023-04-07

1.简介

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,fifo在FPGA内部是RAM加上已编写好的读写控制模块(RTL级)然后“封装”在一起的一个module。他与普通存储器的区别是没有外部读写地址线,这样使…

基于K7的PXIPXIe数据处理板(Kintex-7 FMC载板)

基于PXI&PXIe总线架构的高性能数据预处理FMC 载板,板卡具有 1 个 FMC(HPC)接口,1 个 X8 PCIe 和1个PCI主机接口;板卡采用 Xilinx 的高性能 Kintex-7 系列 FPGA 作为实时处理器,实现 FMC 接口数据的采集…

ASIC-WORLD Verilog(16)综合

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----Asic-World网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加点自己的理解)分享给大家。 这是网站原文&…

Verilog实现2进制码与BCD码的互相转换

1、什么是BCD码?

BCD码是一种2进制的数字编码形式,用4位2进制数来表示1位10进制中的0~9这10个数。这种编码技术,最常用于会计系统的设计里,因为会计制度经常需要对很长的数字做准确的计算。相对于一般的浮点式记数法,…

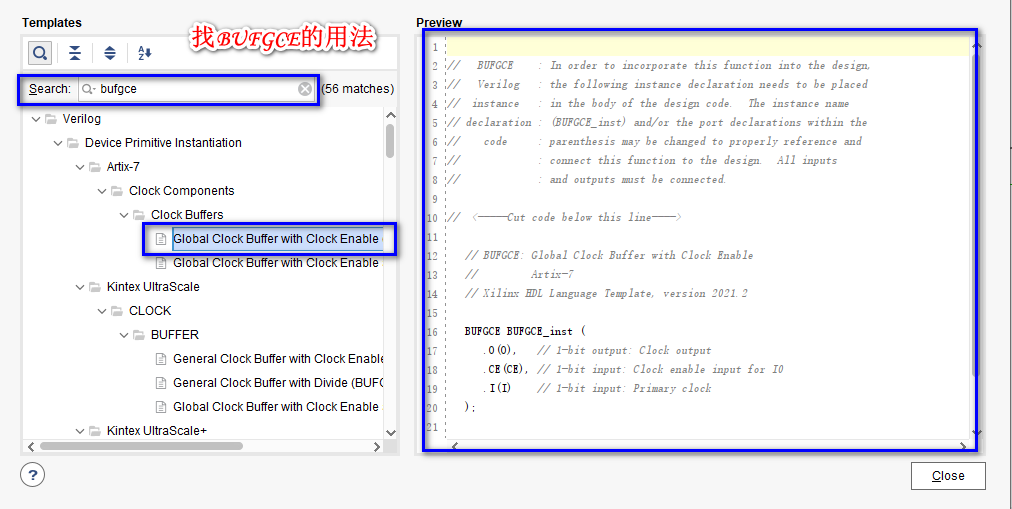

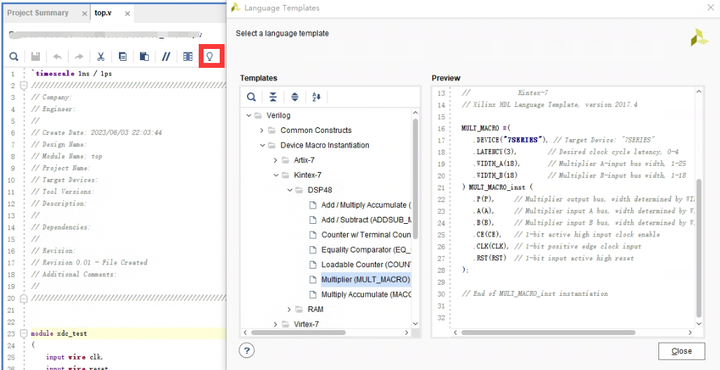

好的FPGA编码风格(2)--多参考设计软件的语言模板(Language Templates)

什么是语言模板? 不论是Xilinx的Vivado,还是Altera的Quartus II,都为开发者提供了一系列Verilog、SystemVerilog、VHDL、TCL、原语、XDC约束等相关的语言模板(Language Templates)。 在Vivado软件中,按顺序…

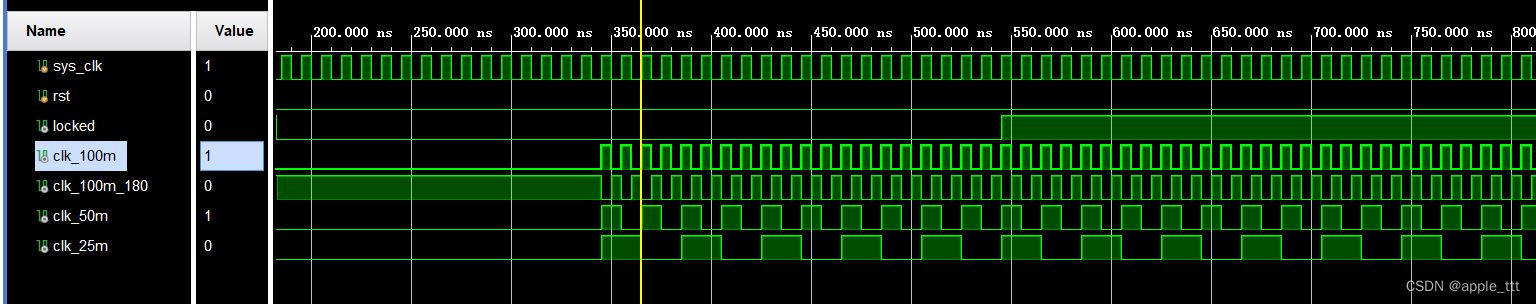

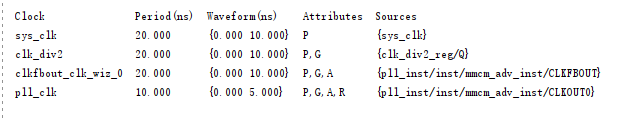

FPGA原理与结构(16)——时钟IP核的使用与测试

系列文章目录:FPGA原理与结构(0)——目录与传送门 一、前言 本文介绍xilinx的时钟IP核 Clocking Wizard v6.0的具体使用与测试过程,在学习一个IP核的使用之前,首先需要对于IP核的具体参数和原理有一个基本的了解&#…

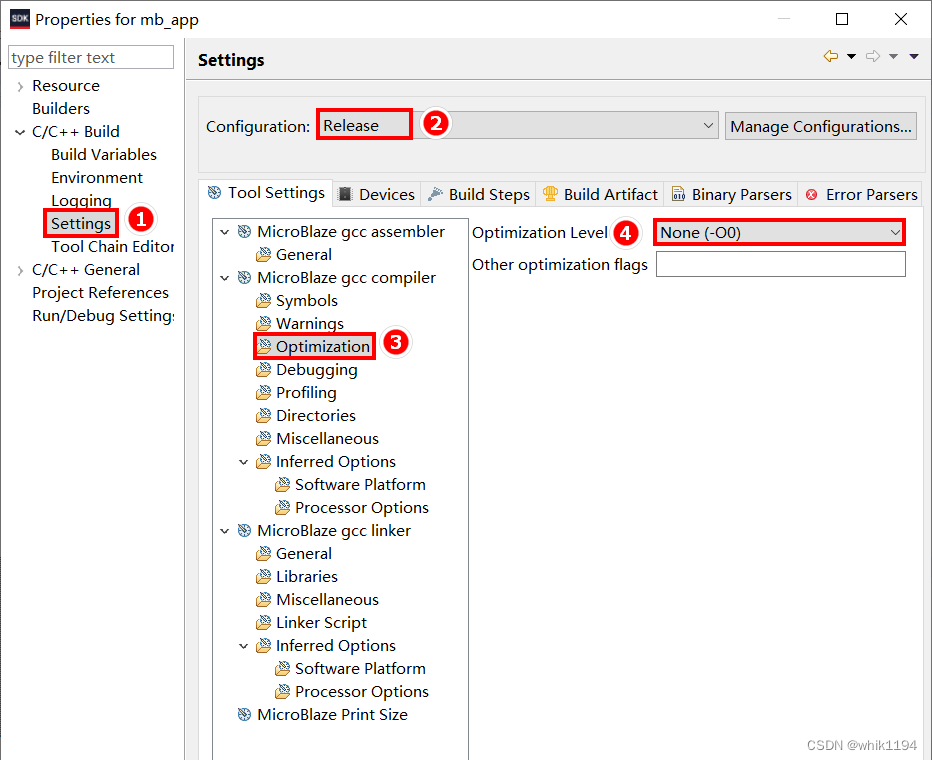

Xilinx MicroBlaze定时器中断无法返回主函数问题解决

最近在使用Xilinx 7系列FPGA XC7A100T时,运行MicroBlaze软核处理器,添加了AXI TIMER IP核,并使能定时器溢出中断,发现定时器触发中断后,无法返回主函数的问题,最后发现修改编译器优化等级就正常了。

FPGA型…

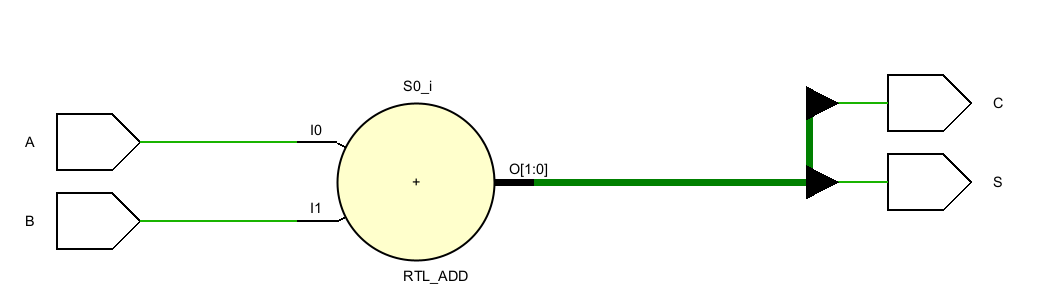

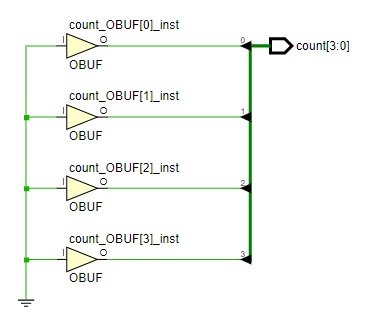

【FPGA】Verilog描述电路的三种方式(结构化、数据流和行为化)

前言

众所周知,Verilog是作为一种HDL(Hardware Description Language,硬件描述语言)出现的,它的主要功能是在不同的抽象层级上描述电路,从而实现电路设计。那么到底该如何描述电路?Verilog提供…

一个简单的驱动开发例程——GPIO流水灯(vivado工程)

前言

本例程基于Xilinx公司的zynq系列zedboard开发板。(其他芯片类似,只需简单修改) 使用Vivado、XSDK与Petalinux工具。 最终效果是:在串口终端运行自己写的app,实现开发板上的流水灯控制。

【一个简单的驱动开发例…

Verilog Tutorial(10)如何实现可复用的Verilog设计?

本文将讨论可以用来实现代码可复用性的参数parameter和generate语句(生成语句)。与大多数编程语言一样,设计者也应该尽量使verilog代码尽可能地具备可复用性----这能够减少未来项目的开发时间,因为设计者可以更轻松地将代码从一个…

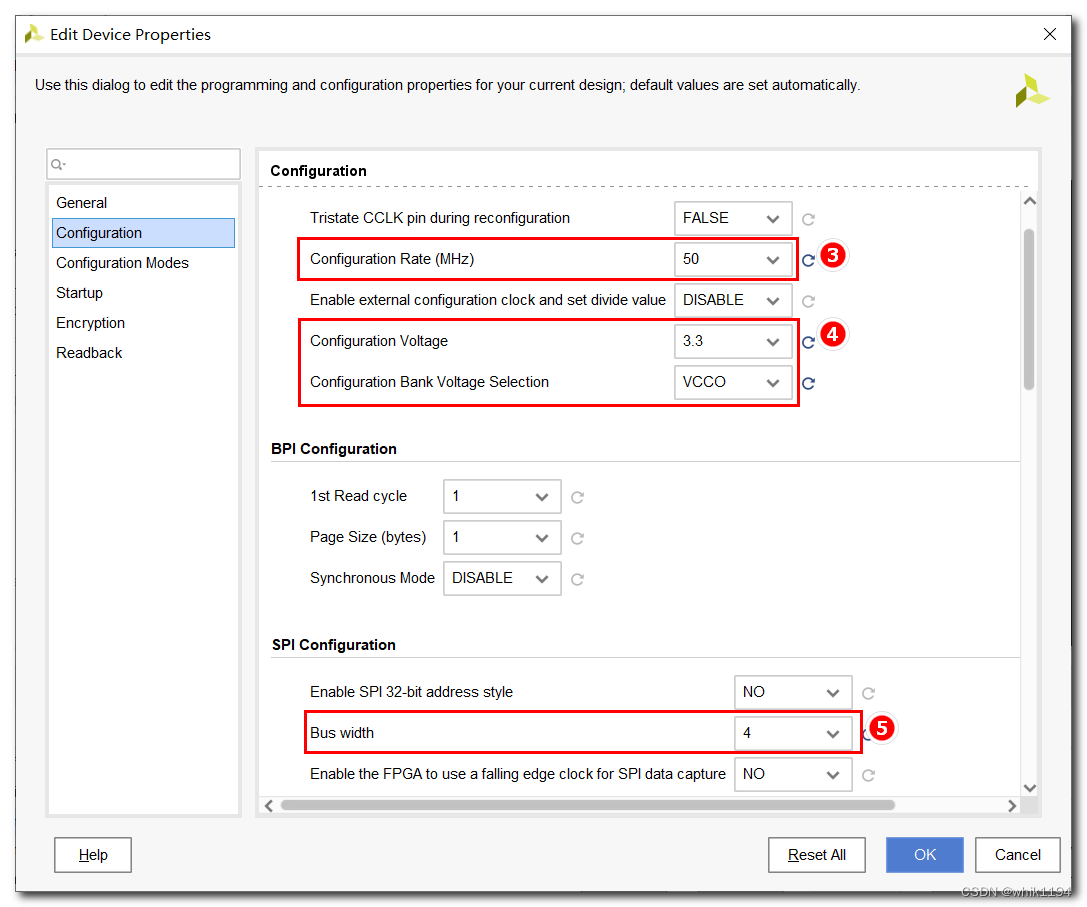

Xilinx FPGA SPIx4 配置速度50M约束语句(Vivado开发环境)

qspi_50m.xdc文件:

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property CONFIG_VOLTAGE 3.3 [curren…

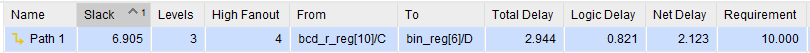

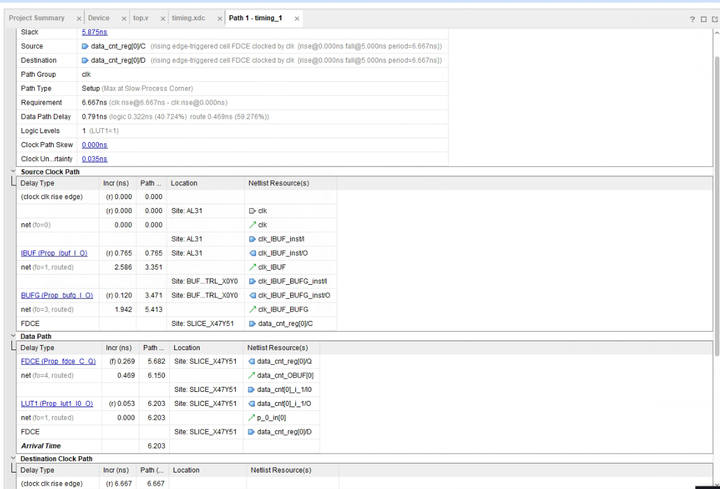

FPGA时序约束--实战篇(读懂Vivado时序报告)

目录

一、新建工程

二、时序报告分析

1、打开时序报告界面

2、时序报告界面介绍

3、时序路径分析

三、总结 FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

本文将详细介绍如何读懂…

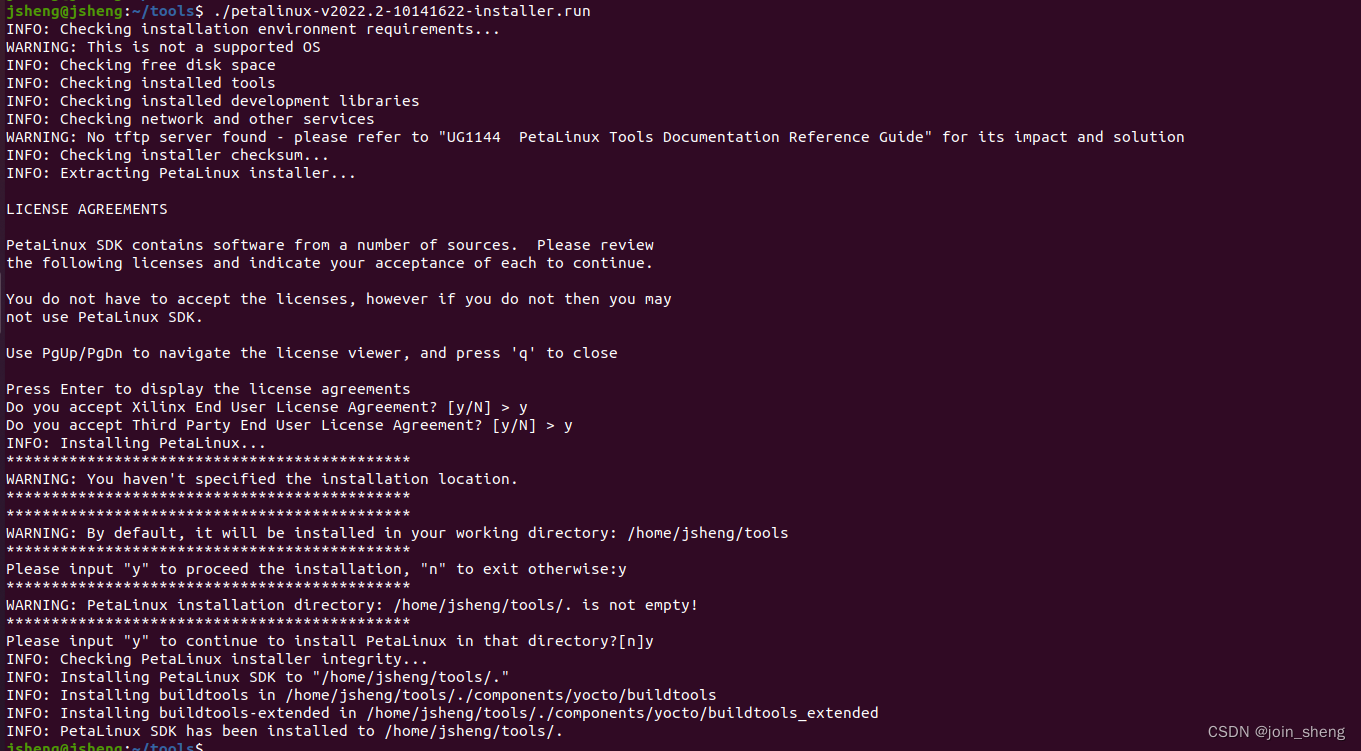

petalinux2022.2在ubantu20.04下的安装

1.Petalinux的下载路径 Downloads 这个是下载petalinux的官网路径。默认是2022.2版本,后期更新的均是以petalinux2022.2版本做的更新。

2.安装流程 在官网下载完成之后,会得到一个名为petalinux-v2022.2-10141622-installer.run的文件,这个文…

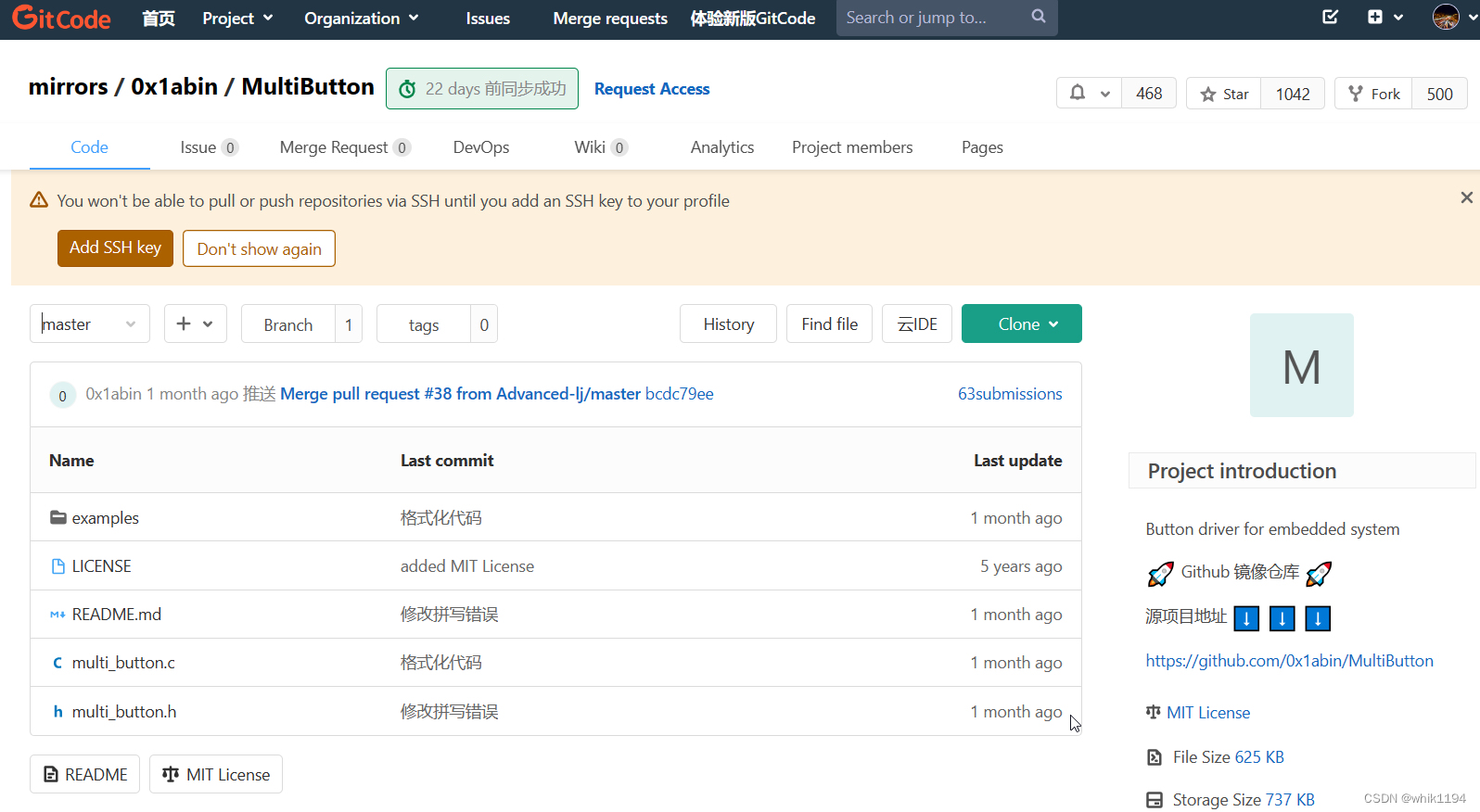

高云FPGA系列教程(11):MultiButton按键驱动模块移植

文章目录 1. MultiButton简介2. MultiButton代码获取3. MultiButton移植4. 测试与运行本文是高云FPGA系列教程的第11篇文章。 1. MultiButton简介

MultiButton, 一个小巧简单易用的事件驱动型按键驱动模块,可无限量扩展按键,按键事件的回调异步处理方式可以简化你的程序结构…

【高云FPGA系列教程(11):MultiButton按键驱动模块移植】

文章目录 1. MultiButton简介2. MultiButton代码获取3. MultiButton移植4. 测试与运行本文是高云FPGA系列教程的第11篇文章。 1. MultiButton简介

MultiButton, 一个小巧简单易用的事件驱动型按键驱动模块,可无限量扩展按键,按键事件的回调异步处理方式可以简化你的程序结构…

基于Xlinx的时序分析与约束(5)----衍生时钟约束

衍生时钟约束语法 衍生时钟(Generated Clocks,又称为生成时钟)是指由设计中已有的主时钟通过倍频、分频或者相移等操作后产生的新的时钟信号,如由MMCM或PLL或由组合逻辑生成的倍、分频时钟信号。 衍生时钟约束必须指定时钟源&…

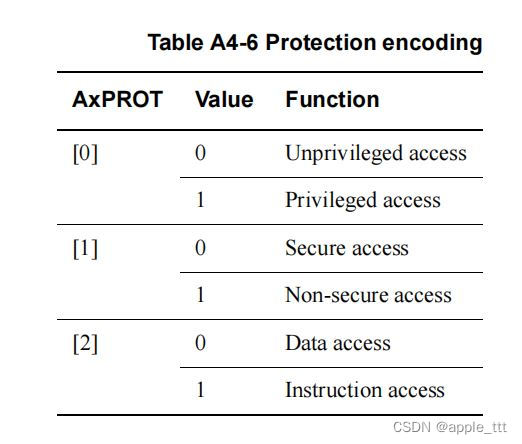

深入浅出AXI协议(6)——传输属性

一、前言 在之前的文章中,我们介绍的主要内容是AXI协议的数据读写结构和读写响应结构,主要讲述了当遇到各种特殊情况时,AXI如何完成数据的读写操作,最后介绍了读写响应的4种类型。 在本文中,我们将介绍AXI协议的传输属性。

二、传…

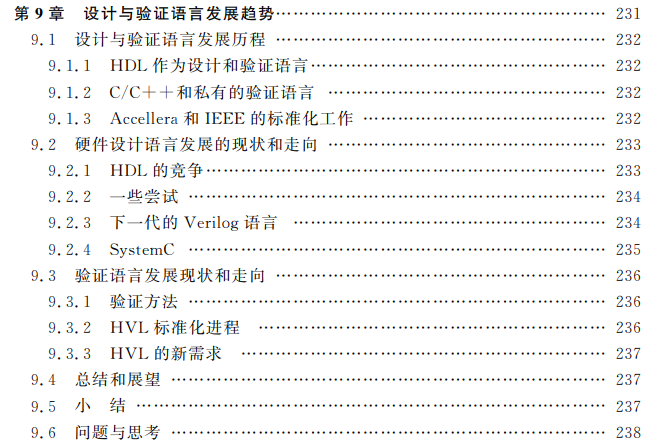

【数字IC/FPGA】书籍推荐(1)----《轻松成为设计高手--Verilog HDL实用精解》

在下这几年关于数字电路、Verilog、FPGA和IC方面的书前前后后都读了不少,发现了不少好书,也在一些废话书上浪费过时间。接下来会写一系列文章,把一部分读过的书做个测评,根据个人标准按十分制满分来打分分享给大家。 书名…

【DDR】基于Verilog的DDR控制器的简单实现(一)——初始化

在FPGA中,大规模数据的存储常常会用到DDR。为了方便用户使用,Xilinx提供了DDR MIG IP核,用户能够通过AXI接口进行DDR的读写访问,然而MIG内部自动实现了许多环节,不利于用户深入理解DDR的底层逻辑。

本文以美光(Micro…

AMD收购Xilinx,Intel收购Altera,FPGA将何去何从?

未来,或许FPGA将被整合到异构多核处理器继续发光发热。 一、AMD收购Xilinx 美国时间2月14日,AMD宣布以全股份交易(all-stock transaction)方式完成对赛灵思(Xilinx)的收购。收购完成后,赛灵思股…

Xilinx ZYNQ系列10款型号IDCODE汇总(2023年7月最新版)

ZYNQ系列产品选型手册:zynq-7000-product-selection-guide

/* Zynq Devices. */

#define IDCODE_XC7Z007 0x03723093

#define IDCODE_XC7Z010 0x03722093

#define IDCODE_XC7Z012 0x0373C093

#define IDCODE_XC7Z014 0x03728093

#defi…

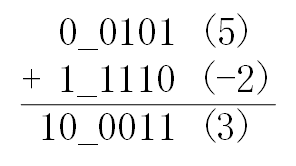

【数字IC/FPGA】什么是无符号数?什么是有符号数?

进制

虽然在日常生活中,我们已经习惯了使用10进制数字,但在由数字电路构成的数字世界中,2进制才是效率更高的选择。

10进制与2进制

10进制(decimal)计数法(一般也叫阿拉伯计数法)是在日常生活…

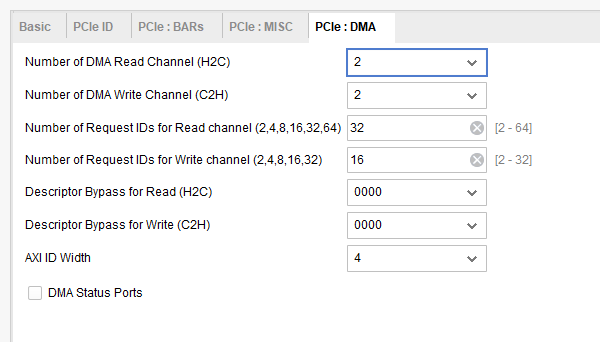

PCIE1—快速实现PCIE接口上下位机通信(一)

1.简介 PCI Express(PCIE)是一种高速串行总线标准,广泛应用于计算机系统中,用于连接主板和外部设备。在FPGA领域中,PCIE也被广泛应用于实现高速数据传输和通信。FPGA是一种灵活可编程的集成电路,可以根据需…

Xilinx Kintex7中端FPGA解码MIPI视频,基于MIPI CSI-2 RX Subsystem架构实现,提供工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优缺点4、详细设计方案设计原理框图OV5640及其配置权电阻硬件方案MIPI CSI-2 RX SubsystemSensor Demosaic图像格式转换Gammer LUT伽马校正VDMA图像缓存AXI4-Stream toVideo OutHDMI输出 5、…

FPGA原理与结构——FIFO IP核的使用与测试

一、前言 本文介绍FIFO Generator v13.2 IP核的具体使用与例化,在学习一个IP核的使用之前,首先需要对于IP核的具体参数和原理有一个基本的了解,具体可以参考:

FPGA原理与结构——FIFO IP核原理学习https://blog.csdn.net/apple_5…

【XILINX】ISE chipscope出现错误 Can‘t load jre bin client jvm.dll

记录一个ISE软件使用过程中遇到的问题及解决方案。

问题

ISE chipscope出现错误 Cant load jre bin client jvm.dll C:\Xilinx\14.7\ISE_DS\ISE\bin\nt C:\Xilinx\14.7\ISE_DS\.xinstall\bin\nt C:\Xilinx\14.7\ISE_DS\.xinstall\bin\nt64 C:\Xilinx\14.7\ISE_DS\ISE\bin\nt6…

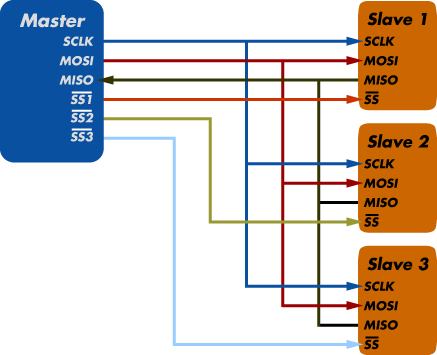

MicroBlaze系列教程(7):AXI_SPI的使用(M25P16)

文章目录 AXI_SPI简介MicroBlaze硬件配置常用函数使用示例波形实测参考资料工程下载本文是Xilinx MicroBlaze系列教程的第7篇文章。 AXI_SPI简介

Xilinx AXI-SPI IP共有两个:一个是标准的AXI_SPI,即4线制SPI,CS、SCLK、MOSI和MISO,另一个是AXI_Quad SPI,支持配置成标准SP…

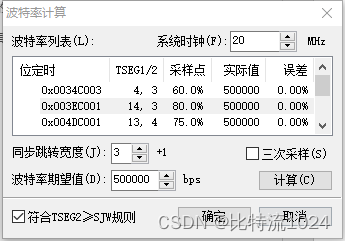

Xilinx microblaze axi can 使用说明

本次主要描述在SDK上如何配置波特率和采样率这两个关键的信息。

XILINX官方提供的驱动包括循环方式和中断方式。配置波特率和采样率主要依靠XCan_SetBaudRatePrescaler和XCan_SetBitTiming这两个函数。主要参数:

#define TEST_BRPR_BAUD_PRESCALAR //分频系…

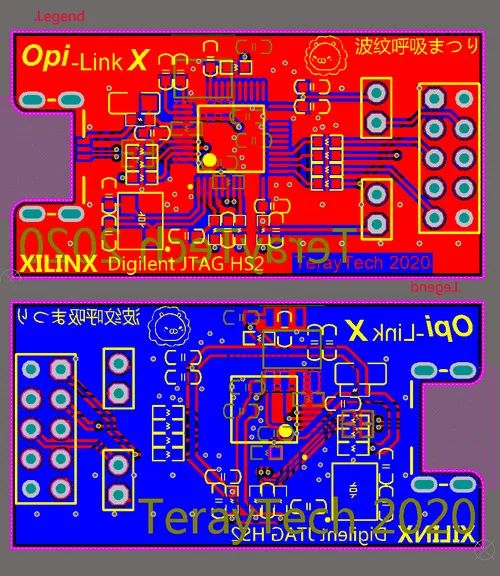

开源、低成本的 Xilinx FPGA 下载器(高速30MHz)

目前主流的Xilinx下载器主要有两种:一种是Xilinx官方出品的Xilinx Platfom Cable USB,还有一个就是Xilinx的合作伙伴Digilent开发的JTAG-HS3 Programming Cable。

JTAG-HS系列最大支持30MHz下载速度,基于FTDI的FT2232方案。 JTAG-HS系列对比…

FPGA高端项目:Xilinx Artix7系列FPGA 多路视频缩放拼接 工程解决方案 提供4套工程源码+技术支持

目录 1、前言版本更新说明给读者的一封信FPGA就业高端项目培训计划免责声明 2、相关方案推荐我这里已有的FPGA图像缩放方案我已有的FPGA视频拼接叠加融合方案本方案的Xilinx Kintex7系列FPGA上的ov5640版本本方案的Xilinx Kintex7系列FPGA上的HDMI版本 3、设计思路框架设计框图…

FPGA时序约束系列文章汇总

时序约束在FPGA开发中起着非常关键的作用。

与时序约束相关的方面包括时钟分析、路径分析、布线和布局优化等。时序约束的正确性和准确性对于设计的成功是至关重要的,因为它们对电路的时序性能、功耗和资源利用率有着重要影响。

有效的时序约束可以帮助设计人员充…

FPGA时序约束--实战篇(时序收敛优化)

目录

一、模块运行时钟频率

二、HDL代码

1、HDL代码风格

2、HDL代码逻辑优化

三、组合逻辑层数

1、插入寄存器

2、逻辑展平设计

3、防止变量被优化

四、高扇出

1、使用max_fanout

2、复位信号高扇出

五、资源消耗

1、优化代码逻辑,减少资源消耗。

2、…

[FPGA IP系列] FPGA常用存储资源大全(RAM、ROM、CAM、SRAM、DRAM、FLASH)

本文主要介绍FPGA中常用的RAM、ROM、CAM、SRAM、DRAM、FLASH等资源。

一、RAM

RAM(Random Access Memory)是FPGA中最基本和常用的内部存储块,根据不同架构可以实现不同容量,最大可达几十Mb。

FPGA中的RAM主要包括: 分布式RAM:存在于逻辑块…

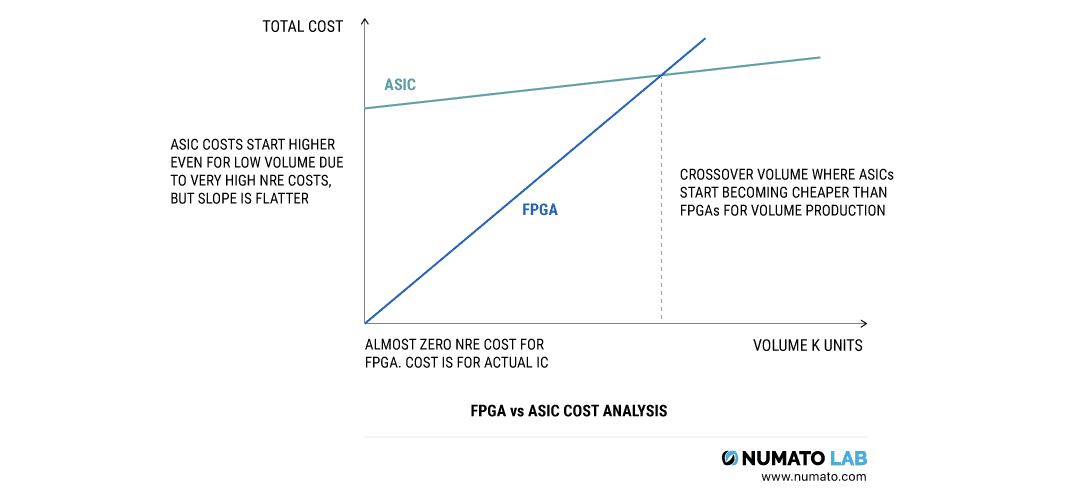

FPGA与ASIC有什么差异?二者该如何选用?

前言 对于一个数字电路的新手来说,这可能是会经常遇到的一个问题:FPGA和ASIC之间的区别是什么? 接下来本文将尝试讲解 “什么是FPGA?” 和 “什么是ASIC?”,然后讲述一些关于FPGA和ASIC的问题,例如它们之间…

14025.ZynqMP System Monitors 监控模块

文章目录 1 背景2 ZynqMp System Monitors2.1 Introduction2.2 Features2.3 PLSYSMON Module2.4 PSSYSMON Module2.5 编程示例1 背景 本文背景需要获取ZynqMp 的PS温度、PL温度,以及在PL sysmon 部分,VP_VN 外接有pmic采集的电压。参考xilinx手册 ug1085, ug1087,ug580.2 Zyn…

ASIC-WORLD Verilog(5)基础语法下篇

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…

Vivado XADC IP核 使用详解

本文介绍Vivado中XADC Wizard V3.3的使用方法。

XADC简介 XADC Wizard Basic

Interface Options: 一共三种,分别是AXI4Lite、DRP、None。勾选后可在界面左侧看到相应通信接口情况。Startup Channel Selection Simultaneous Selection:同时监…

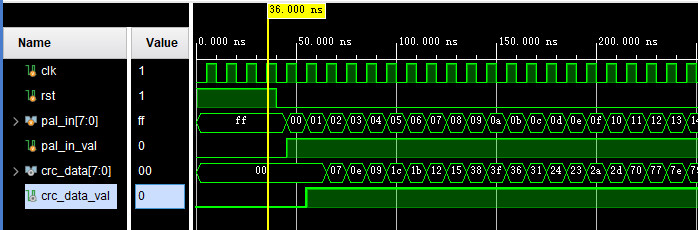

【FPGA/IC】CRC电路的Verilog实现

前言

在通信过程中由于存在各种各样的干扰因素,可能会导致发送的信息与接收的信息不一致,比如发送数据为 1010_1010,传输过程中由于某些干扰,导致接收方接收的数据却成了0110_1010。为了保证数据传输的正确性,工程师们…

FPGA高端项目:Xilinx Artix7 系列FPGA纯verilog图像缩放工程解决方案 提供4套工程源码和技术支持

目录 1、前言版本更新说明给读者的一封信FPGA就业高端项目培训计划免责声明 2、相关方案推荐我这里已有的FPGA图像缩放方案本方案在Xilinx Kintex7 系列FPGA上的应用本方案在国产FPGA紫光同创系列上的应用本方案在国产FPGA高云系列上的应用 3、设计思路框架设计框图视频源选择o…

如何做到一套FPGA工程无缝兼容两款不同的板卡?

试想这样一种场景,有两款不同的FPGA板卡,它们的功能代码90%都是一样的,但是两个板卡的管脚分配完全不同,一般情况下,我们需要设计两个工程,两套代码,之后还需要一直维护两个版本。

那么有没有一种自动化的方式,实现一个工程,编译出一个程序文件,下载到这两个不同的板…

【DDR】DDR4学习记录

这里以美光DDR4芯片 MT40A512M16HA-075E datasheet 为例,说明DDR4存储器的原理及仿真。 根据开发板手册ug1302,在vcu128(xcvu37p)开发板上,共具有5块DDR4芯片,在数据信号上4块DDR4具有16位数据线&#…

Xilinx FPGA平台DDR3设计详解(一):DDR SDRAM系统框架

DDR SDRAM(双倍速率同步动态随机存储器)是一种内存技术,它可以在时钟信号的上升沿和下降沿都传输数据,从而提高数据传输的速率。DDR SDRAM已经发展了多代,包括DDR、DDR2、DDR3、DDR4和DDR5,每一代都有不同的…

ASIC-WORLD Verilog(6)运算符

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…

【FPGA】正确处理设计优先级--或许能帮你节省50%的资源

概述

假如现在有一种方法–可以在不怎么需要修改已有设计的情况下,就可以帮您节省50%的设计资源,那你会试试看吗?

当前市场环境下,更低廉的成本却可获得同等性能无疑是极具诱惑的。本文将介绍一种FPGA设计技术,该技术…

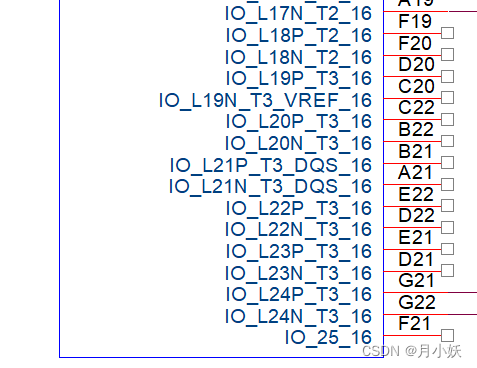

XILINX 7系列FPGA普通IO与差分IO

🏡《Xilinx FPGA开发宝典》 目录 1,概述2,IO说明3,总结 1,概述 本文介绍XILINX 7系列FPGA普通IO和差分IO的识别方法与注意事项。 2,IO说明 7系列FPGA的绝大多数IO均支持差分,但是有些IO是不支持…

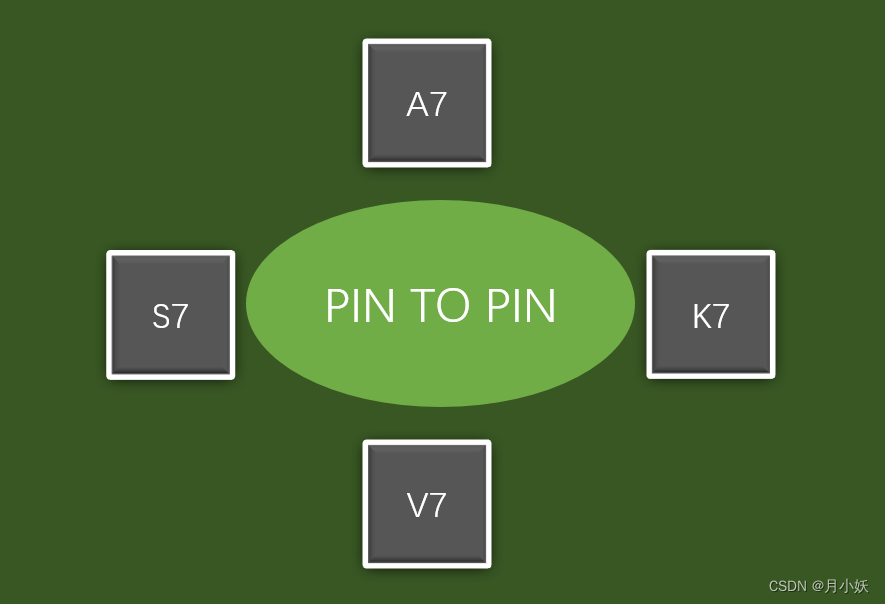

XILINX 7系列FPGA封装兼容原则及同封装替换注意问题

🏡《电子元器件高级指南》 目录 1,概述2,封装兼容原则3,注意问题4,总结 1,概述 XILINX 7系列的FPGA同封装的元器件一般都是可以兼容的,在一定程度上可以做到PIN TO PIN的替换,本文介…

J1—Vivado调试技巧VIO IP

1.简介

VIO(Virtual Input/Output)IP核是一种用于FPGA设计的IP核,它可以模拟输入/输出设备的功能,如键盘、鼠标、显示器等。VIO IP核可以在FPGA设计中用于调试和验证,帮助工程师快速定位问题并进行调试。如图所示&…

ASIC-WORLD Verilog(3)第一个Verilog代码

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的Verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文…

FPGA可重配置原理及实现(2)——要求与标准

一、前言 在之前的文章中着重介绍了FPGA的可重构技术,可重配置技术是Xilinx提供的用来高效利用FPGA设计资源实现FPGA资源可重复利用的最新的FPGA设计技术,这种技术的发展为FPGA应用提供了更加广阔的前景。在此基础上,我们简单介绍了与此技术相…

FPGA可重配置原理及实现(1)——导论

一、概述 可重配置技术是Xilinx提供的用来高效利用FPGA设计资源实现FPGA资源可重复利用的最新的FPGA设计技术,这种技术的发展为FPGA应用提供了更加广阔的前景。 术语“重构”是指FPGA已经配置后的重新编程。FPGA的重构有两种类型:完全的和部分的。完全重…

【Vitis】Vitis性能优化的开源库

Vitis HLS简介 Vitis™HLS是一种高层次综合工具,支持将C、C和OpenCL™函数硬连线到器件逻辑互连结构和RAM/DSP块上。

Vitis HLS可在Vitis应用加速开发流程中实现硬件内核,并使用C/C语言代码在VivadoDesign Suite中为赛灵思器件设计开发RTL IP。 【Vitis…

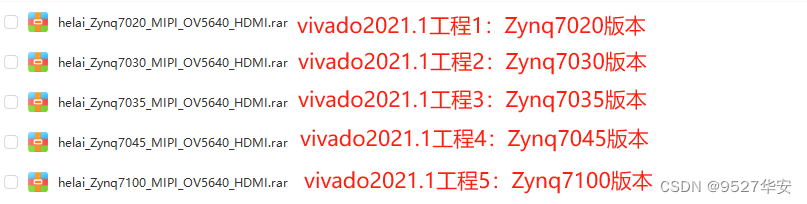

Xilinx Zynq 7000系列中端FPGA解码MIPI视频,基于MIPI CSI-2 RX Subsystem架构实现,提供5套工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优缺点4、详细设计方案设计原理框图OV5640及其配置权电阻硬件方案MIPI CSI-2 RX SubsystemSensor Demosaic图像格式转换Gammer LUT伽马校正VDMA图像缓存AXI4-Stream toVideo OutHDMI输出 5、…

【FPGA图像处理实战】- 图像处理前景如何?就业前景如何?

图像处理是FPGA应用的主要领域之一,图像处理数据量特别大且对实时性处理要求高的场景,这恰好能发挥FPGA流水线可实时处理的优势。

那么FPGA图像处理的前景如何?

一、FPGA开发(图像处理)招聘就业情况

看FPGA图像处理前景,最简单的方式--我们去招聘网站上搜一搜,看看招…

【FPGA图像处理实战】- 彩色图像灰度化

今天介绍一下图像处理中的基础算法--彩色图像灰度化。

一、彩色图像处理灰度化

彩色图像灰度化是一种将彩色图像转换为灰度图像的过程。

在RGB模型中,如果R=G=B时,则彩色表示一种灰度颜色,其中R=G=B的值叫灰度值。

因此,灰度图像每个像素只需一个字节存放灰度值(又称强…

vivado中文乱码更换中文等宽字体

tools-setting-fonts 选择 monospace 支持中文的等宽字体。修改系统自带的consolas(Consolas-with-Yahei-master),该字体和原来的consolas重名,需要覆盖原来的字体。原介绍如下:( Different From "Yah…

FPGA原理与结构——时钟IP核的使用与测试

一、前言 本文介绍xilinx的时钟IP核 Clocking Wizard v6.0的具体使用与测试过程,在学习一个IP核的使用之前,首先需要对于IP核的具体参数和原理有一个基本的了解,具体可以参考:

FPGA原理与结构——时钟IP核原理学习https://blog.c…

Xilinx FPGA芯片内部时钟和复位信号使用(Spartan-6、Artix-7和Kintex-7)

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

Spartan-6系列

wire clk_50m;

wire rst_n;STARTUP_SPARTAN6 STARTUP_SPARTAN6_inst (.CFGMCLK(clk_50m), // …

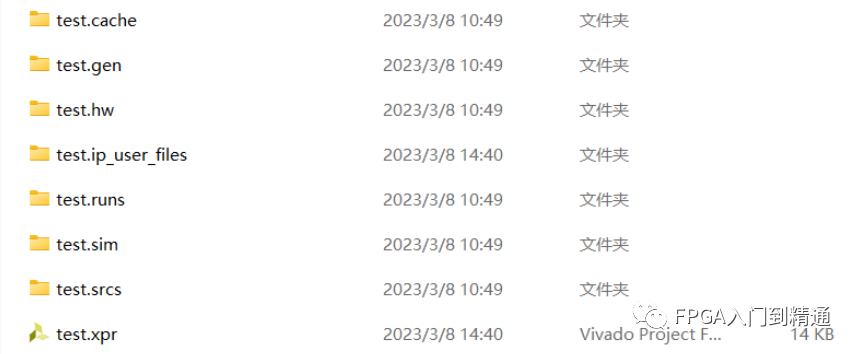

Vivado如何清理工程,并避免缺失必要的文件?

FPGA开发是一项非常复杂的工作,需要处理大量的代码、约束和仿真文件。在开发过程中,由于文件数量庞大,很容易导致工程变得混乱不堪。Vivado是Xilinx公司推出的一款FPGA开发工具,能够帮助开发人员处理这种复杂性,提高开…

ISE与Notepad++关联

安装Notepad,注意安装目录不要有中文,空格等特殊字符。 打开ISE,打开Edit下的Preferences… 具体设置如下图!!! 打开Editor,选择Custome选项输入安装目录(Notepad的绝对地址&#x…

浅谈Altera和Xilinx的FPGA区别

对于Altera和Xilinx的FPGA,可以分为两个方面去比较一下,基本逻辑资源和内部基本架构。 从目前企业中做开发使用的广泛性来说,Xilinx占得比重确实是大一些,但是从其他方面来说,比如价格,相对而言Altera的…

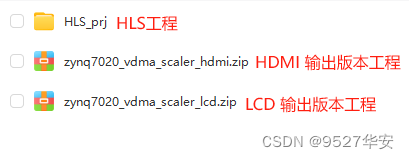

Xilinx Zynq-7000系列FPGA任意尺寸图像缩放,提供两套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐FPGA图像处理方案FPGA图像缩放方案 3、设计思路详解HLS 图像缩放介绍 4、工程代码1:图像缩放 HDMI 输出PL 端 FPGA 逻辑设计PS 端 SDK 软件设计 5、工程代码2:图像缩放 LCD 输出PL 端 FPGA 逻辑设计PS 端 SDK 软件设…

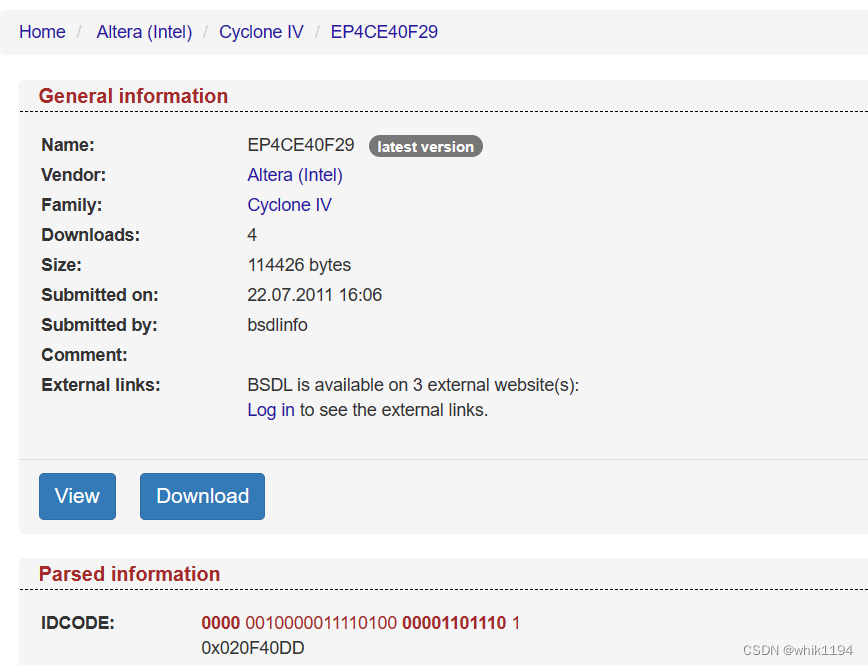

获取Xilinx FPGA芯片IDCODE的4种方法(支持任何FPGA型号)

文章目录 方式1:官方文档方式2:一个头文件方式3:BSDL文件方法4:芯片IDCODE在线搜索网站Xilinx FPGA部分型号IDCODE汇总 方式1:官方文档

对于常用的Spartan-6系列可以在UG380文档中找到对应的IDCODE,Sparta…

xilinx FPGA multi boot之镜像切换

最近做的了一个无线通信的项目,需要在同一套设备上实现两套不同的波形软件,因为FPGA的逻辑资源不够同时放下两套代码,因此采用了镜像切换的方式来实现,xilinx的专业术语叫multi boot功能 。意思是在一片Flash中的不同地址放两个代…

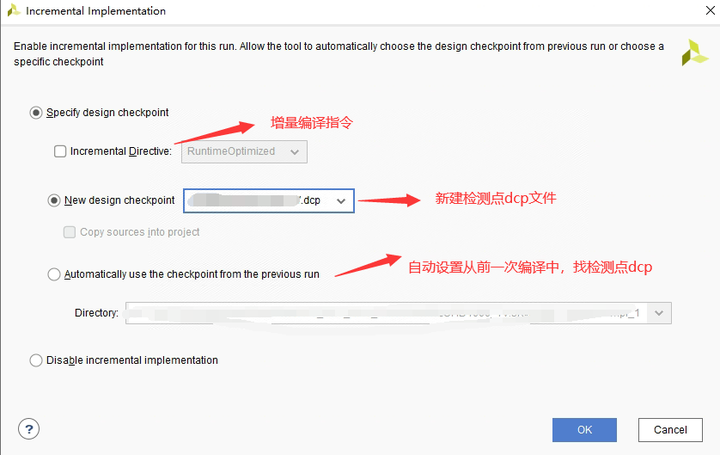

Vivado增量编译:加速FPGA设计实现的利器

随着FPGA设计的复杂度不断提高,设计人员需要选择更为高效的设计流程来保证开发效率和减少开发成本。其中,Vivado增量编译是一种非常重要的设计流程。本文将介绍Vivado增量编译的基本概念、优点、使用方法以及注意事项。

通过阅读本文可以了解࿱…

FPGA输出lvds信号点亮液晶屏

1 概述 该方案用于生成RGB信号,通过lvds接口驱动逻辑输出,点亮并驱动BP101WX-206液晶屏幕。 参考:下面为参考文章,内容非常详细。Xilinx LVDS Output——原语调用_vivado原语_ShareWow丶的博客http://t.csdn.cn/Zy37p 2 功能描述 …

Xilinx Zynq-7000系列FPGA多路视频处理:图像缩放+视频拼接显示,提供工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐FPGA图像处理方案FPGA图像缩放方案FPGA视频拼接叠加融合方案推荐 3、设计思路详解HLS 图像缩放介绍Video Mixer介绍 4、vivado工程介绍PL 端 FPGA 逻辑设计PS 端 SDK 软件设计 5、工程移植说明vivado版本不一致处理FPGA型号不一致处理其他…

基于ZCU106平台部署Vitis AI 1.2/2.5开发套件【Vivado+Vitis+Petalinux2020/2022】

Vitis AI是 Xilinx 的开发平台,适用于在 Xilinx 硬件平台(包括边缘设备和 Alveo 卡)上进行人工智能算法推理部署。它由优化的IP、工具、库、模型和示例设计组成。Vitis AI以高效易用为设计理念,可在 Xilinx FPGA 和 ACAP 上充分发…

[FPGA IP系列] 2分钟了解FPGA中的BRAM

FPGA设计中,BRAM是一项非常关键的内置存储资源,FPGA开发需要熟练使用BRAM,今天再复习一下BRAM的知识,包括BRAM的定义、组成、应用等等。

一、BRAM介绍

1、BRAM的定义

RAM是Random Access Memory,也就是随机访问数据…

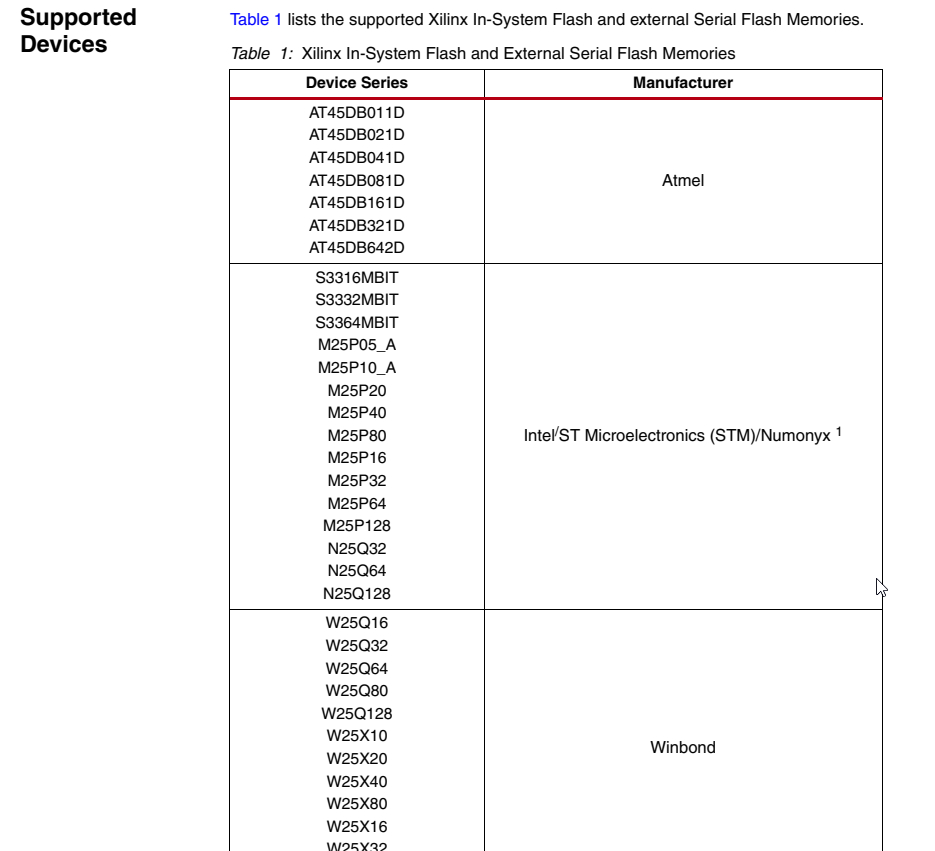

MicroBlaze系列教程(9):xilisf串行Flash驱动库的使用

文章目录 1. xilisf库简介2. xilisf库函数3. xilisf配置4. xilisf应用示例工程下载本文是Xilinx MicroBlaze系列教程的第9篇文章。 1. xilisf库简介

xilisf库(Xilinx In-system and Serial Flash Library) 是Xilinx 提供的一款串行Flash驱动库,支持常用的 Atmel 、Intel、S…

![[FPGA IP系列] BRAM IP参数配置与使用示例](https://img-blog.csdnimg.cn/img_convert/bb90386cec9df272311537322199e691.png)

![[FPGA IP系列] 2分钟了解FPGA中的BRAM](https://img-blog.csdnimg.cn/b4c99a625a2c4f84a061586a235d883d.png)